MIPI Controller IP for SMIC

Welcome to the ultimate MIPI Controller IP for SMIC hub! Explore our vast directory of MIPI Controller IP for SMIC

All offers in

MIPI Controller IP

for SMIC

Filter

Compare

9

MIPI Controller IP

for SMIC

from 2 vendors

(1

-

9)

-

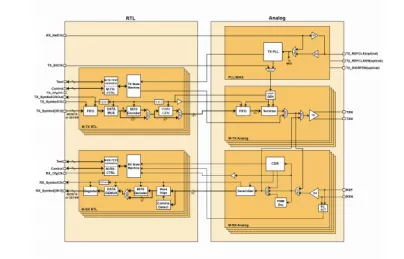

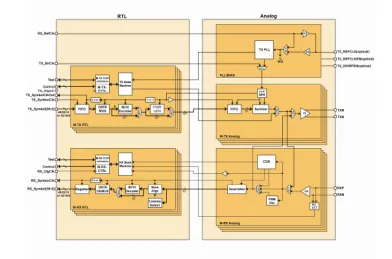

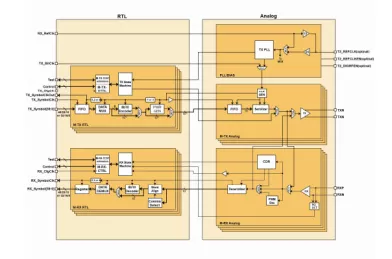

MIPI M-PHY in SMIC 90LL

- Supports MIPI Standard for M-PHY v3.0.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

-

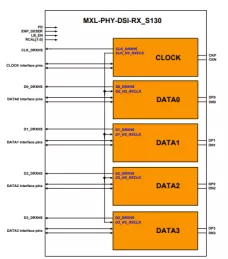

MIPI D-PHY DSI RX (Receiver) in SMIC 130nm

- SMIC 130nm

- Consists of 1 Clock lane and 4 Data lanes

- Supporting the MIPI Standard 1.1 for D-PHY

-

MIPI M-PHY in SMIC 130nm

- Complies with MIPI Standard for M-PHY v3.0

- Slew-rate control for EMI reduction

- Supports HS modes GEAR 1-3

-

MIPI M-PHY Compliant (HS-G2) IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports all HS modes (GEAR 1-2)

-

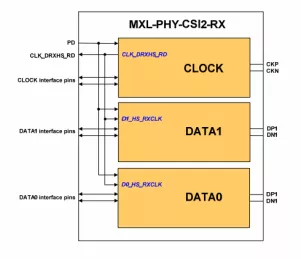

MIPI D-PHY CSI-2 RX (Receiver) IP

- Consists of 1 Clock lane and 2 Data lanes

- Complies with MIPI Standard 1.0 for D-PHY

- Supports both high speed and low-power modes

- 80 Mbps to 1Gbps data rate in high speed mode

-

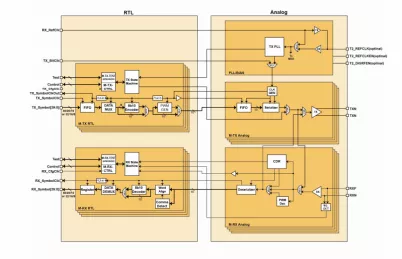

MIPI M-PHY DigRF Compliant IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.00- r02 and DigRF v4 V1.10.00.0.04

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS mode (GEAR 1-2, A & B)

-

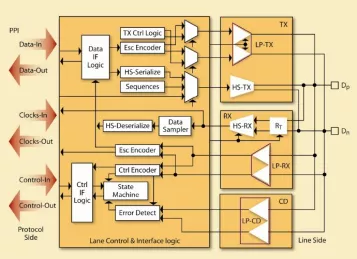

MIPI D-PHY Universal IP

- Complies with MIPI Standard for D-PHY V1.0

- Point-to-point differential interface supporting multiple data lanes and a clock lane

- Supports both high speed and low-power modes

- Data lanes support both bidirectional and unidirectional modes

-

MIPI CSI-2 TX IP

- Compliant with MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2) V1.3

- Compliant with MIPI Alliance Standard for D-PHY Specifications V1.2

- Integrated PHY Protocol Interface (PPI) interfaces to CSI-2 and UniPro™ MIPI® protocols

- HS, LP and ULPS modes supported

-

MIPI CSI-2 RX IP

- Compliant with MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2) V1.3

- Compliant with MIPI Alliance Standard for D-PHY Specifications V1.2

- Integrated PHY Protocol Interface (PPI) interfaces to CSI-2 and UniPro™ MIPI® protocols

- HS, LP and ULPS modes supported