Ethernet 10G KR Serdes

Overview

The VHT1T28KR10 is an enhanced multi-lane 10G Ethernet Hard macro that is compatible with data transfer capabilities up to 10Gbps(10GBASEKR) and XAUI. It is designed with a standard multilane interface to the core side. It has the added advantage of not requiring an external resistor, hence saving area at the system level and a pin at the chip level.

Key Features

- Quad Channel Multi Lane Macro

- Integrated backplane PCS, PMA layer

- High-Speed Data Transfer

- Up-to 10Gbps per lane

- Support for Link Training, FEC, Auto-Negotiation

- High performance system interface

- SDR XGMII interfaces to 1G/10G Transmit De-emphasis and Receive Adaptive Equalization

- Supported Lane widths of x1, x2, x4

- Encoding standards: 64b/66b

- Simple configuration interface

- Small register configuration space

- Simple interface, can be easily connected to a standard APB bus, or similar

- Minimal setup, with automatic start-up when reset is de-asserted

- On-Chip IO ring compatibility

- Small footprint

- Flip-Chip packaging

- Clocking

- Multiple clocking options with external reference clock or internal clock for debug

- Extensive Test and Debug Features

- Virtual Eye generation

- Loopback Serial and parallel

- Scan

- JTAG, IEEE 1149.1

- Serial Debug

- Embedded TAP controller

- Configurability

- Programmable lane enable/disable

- Choice of macros pre-configured for 1 to 4 lanes

- Low Power

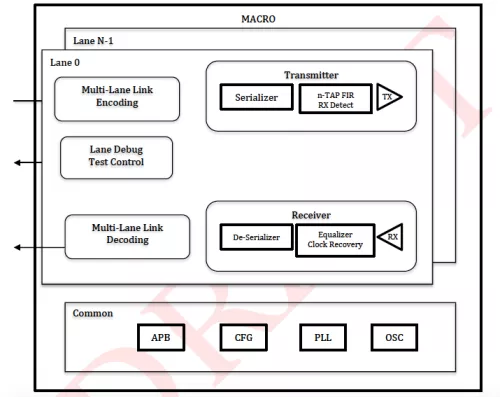

Block Diagram

Technical Specifications

Foundry, Node

28nm 40nm 65nm 22nm

Maturity

Multiple customers have used

Availability

Immediately

Related IPs

- Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- 10G to 400G High Speed Channelized Ethernet Controller MAC/PCS/FEC

- 10G to 400G High Speed Ethernet Controller MAC/PCS/FEC

- 10G Combo Serdes for USB/PCIe/Ethernet, TSMC 28HPC+, N/S orientation

- 10G Combo Serdes for USB/PCIe/Ethernet, SMIC 14FF, N/S orientation