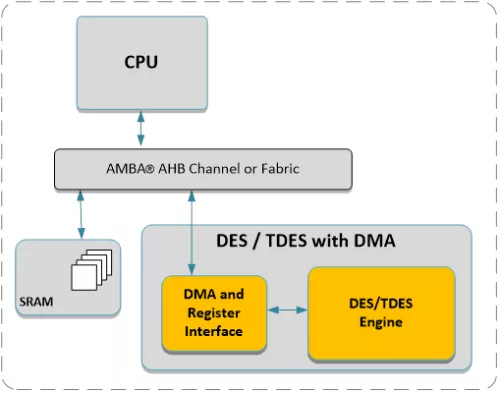

AHB Triple DES with DMA

Overview

The AHB DES/TDES Encryption/Decryption Engine is a configurable core that interfaces to an AHB microprocessor bus. The Controller encrypts or decrypts blocks of data based on the DES encryption standard. In order to accommodate a wide variety of system requirements, the Engine can be generated in two modes: LowLatency and LowGateCount. For a TDES system, three DES cores are instantiated. The table below summarizes the options and how to implement them. The checked definitions should be defined and the definitions not checked should be commented out. In this table LL refers to Low Latency and LGC refers to Low Gate Count.

Key Features

- AHB Master DMA

- AHB Slave Register Interface

- DES/TDES modes supported:

- Electronic Code Book (ECB)

- Cipher Block Chaining (CBC)

- Output Feedback (OF)

- Maskable Interrupt

Block Diagram

Deliverables

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

- C-Sample Code

Technical Specifications

Maturity

Silicon Proven

Availability

now