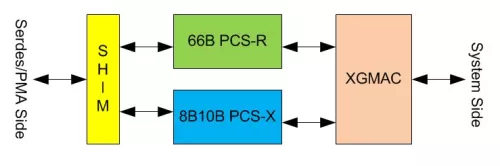

The fully integrated Physical Coding Sublayer (PCS), KR FEC (IEEE Clause 74 – fire code FEC), SGMII / 1000BASE-X and Media Access Controller (MAC) core for 25Gbps, 10Gbps, 2.5Gbps/1.25Gbps Ethernet applications is compliant with IEEE 802.3 standard and SGMII specification. The interface to the PMA supports a single channel Quad-mode bi-directional, serial interface. The PCS sublayer supports both 64/66B encoding (10GE) and 8B10B encoding (SGMII/1000BASE-X) with an optional FEC layer function for backplane (10G-KR) application. This Quad-Mode Core is configurable through software register.

The east-bound interface from the MAC provides a configurable 64-bit system interface.

The bound interface performs the mapping of transmit and receive data streams (at the PMA layer) to the on-chip SERDES.

25GE/10GE/SGMII/1000BASE-X and MAC

Overview

Key Features

- Integrated MAC and PCS for area efficiency

- Fully compatible with IEEE802.3 2015 standard and SGMII specification 1.6 Standard

- Super low latency with minimized fixed and variable delay for network efficiency.

- Supports 1588v2 1-step and 2-step time stamps and full error handling

- Supports 802.1Qbb priority flow control (PFC)

- SGMII/1000BASE-R PCS Core Features

- PCS-X TX Core

- PCS-X encoding of incoming MII signal

- 8B10B encoding

- Disparity calculation

- Auto negotiation TX – enable/restart

- PCS-X RX Core

- 8B10B decoding

- Disparity check

- Auto negotiation RX – sync

- PCS-X decoding and synchronization

- Carrier Extend/Error detection and interrupt reporting

- Performance Monitoring and Statistics

- PCS Status – link up/down

- disparity error count

- 10GBASE-R PCS Core Features

- PCS-R TX Core

- 64B/66B encoding of incoming MII signal

- X58 Scrambling (optional bypass)

- Test pattern generation

- Clause 45 MDIO register set

- PCS-R RX Core

- 64B/66B decoding to MII signal

- Test pattern monitoring

- Clause 45 MDIO register set

- Error detection and interrupt reporting

- Loopback from TX MII to RX MII

- Performance Monitoring and Statistics

- PCS Status – link up/down

- High bit error rate (hi-BER)

- BER counter

- Test pattern error counter

- FC FEC (Optional) Features

- TX path

- 66/65 transcoding

- FC (RS2112,2080) Forward Error Correction (FEC) parity calculation and insertion with symbol distribution

- PN-2112 scrambling

- Clause 45 MDIO register set

- Error detection and interrupt reporting

- RX path

- Reverse 66/65 transcoding

- PN-2112 – Alignment lock

- FC (RS2112,2080) FEC decoding and correction

- Performance Monitoring and Statistics

- FEC Corrected code word count (with FEC enabled)

- FEC corrected 1s and 0s counts

- FEC Uncorrected code word count (with FEC enabled)

- FEC symbol error counter (with FEC enabled)

- Clause 45 MDIO register set

- Error detection and interrupt reporting

- XGMAC/GMAC Core Features

- TX MAC

- TX FCS insertion – programmable control

- TX Preamble insertion – programmable control

- TX test pattern generation

- TX MAC control frame generation

- Unicast/Multicast PAUSE frame generation by MAC client or by software

- Software configurable PAUSE quanta

- TX Performance Monitoring and Statistics (counters are 32-bit with read-to-clear)

- Byte count

- Frame count

- Local PAUSE frame count

- Total PAUSE frame count

- Broadcast frame count

- Multicast frame count

- Unicast frame count

- Bad FCS frame count

- Undersize frame count

- Oversize frame count

- Fragmented frame count

- Jabber frame count

- Frame count statistic for the following sized frames:

- 64 byte

- 65-127

- 128-255

- 256-511

- 512-1023

- 1024-1518

- 1519-2047

- >= 2048

- RX MAC

- RX BER monitor

- RX FCS check and removal

- RX Preamble removal

- RX PAUSE frame processing and handling

- RX Performance Monitoring and Statistics (counters are 32-bit with read-to-clear)

- Drop count

- Byte count

- Frame count

- PAUSE frame count

- Broadcast frame count

- Multicast frame count

- Unicast frame count

- Bad FCS frame count

- Undersize frame count

- Oversize frame count

- Fragmented frame count

- Jabber frame count

- Frame count statistic for the following sized frames:

- 64 byte

- 65-127

- 128-255

- 256-511

- 512-1023

- 1024-1518

- 1519-2047

- >= 2048

- Additional Add-on features

- 1588v2 time stamping

- 802.1Qbb Priority Flow Control (PFC) up to 8 priorities

- TX MAC

- TX path

- PCS-R TX Core

- PCS-X TX Core

Benefits

- Proven IP reduces development time and risk

- Support 10GGBASE-R/KR/XFI and 1000BASE-KX PMD interfaces

- Support 25G/10G/SGMII/1000BASE-X PCS encoding

- Support for a single-lane SERDES interface

- MAC rate at 25G/10G/2.5G/1G

- Optional FC FEC (RS 2112,2080) – IEEE 802.3 Clause 74 support in 10GBASE-KR mode

- Off-the-shelf, proven technology implementation in FPGAs and ASIC SOC

- Tested and interoperability-proven against Spirent and Viavi test equipment

Block Diagram

Applications

- High performance server network interface cards

- Mid-sized routers