Other

All offers in

Other

Filter

Compare

44

Other

from 14 vendors

(1

-

10)

-

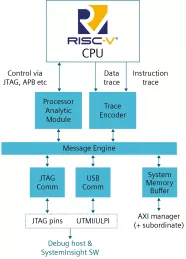

Tessent RISC-V trace and debug

- Instruction trace

- Efficient packet format

- Fast profiling

- Multiple retirement

-

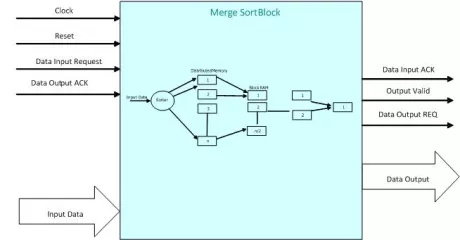

Merge Sort Core

- Optimized design allows customers to target cost efficient FPGAs.

- Can be tailored to customer needs

- Fully synchronous design using only one clock

- Area/Power efficient architecture

-

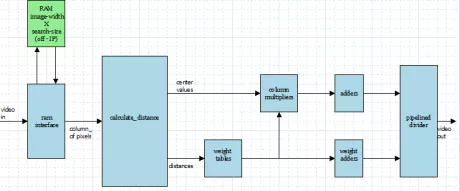

Hardware NLM (Non-Local-Mean) Video Noise Reduction IP core

- parameterized search-window size

- parameterized number of bits per pixel

- efficient implementation

-

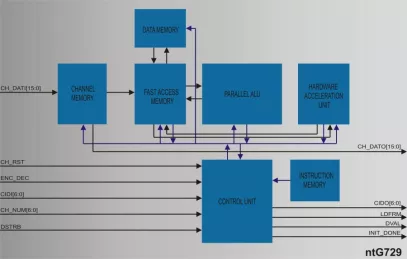

ITU-T G729A Voice Codec Hardware Accelerator

- Voice codec capable of multi-channel 8kbps voice compression based on ITU-T G729A standard.

- Selective Channel initialization.

- AMBA bus support for easy SoC integration.

- Best performance/silicon area ratio available in the industry.

-

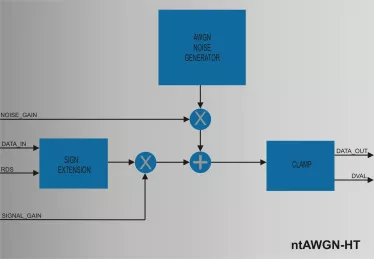

High Throughput Additive White Gaussian Noise Generator

- High precision AWGN Channel emulator.

- Programmable Pseudo Random Generator(LFSR).

- Programmable number of output bits.

- Support of throughput rates up to 10 Gbps.

-

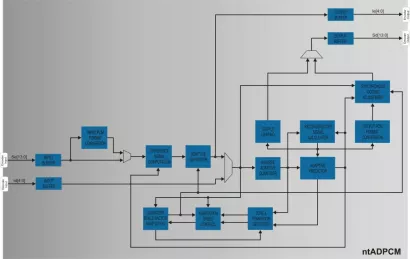

ADPCM G.726 Codec

- Compliant with ITU G.721, G.723, G.726 and G.726-Annex recommendations.

- On-the-fly configuration for variable compression rate, PCM law.

- Process capability of up to 64 full duplex or up to 128 half duplex voice channels.

- Burst and continuous mode support.

-

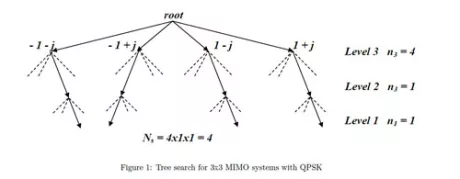

MIMO Sphere Decoder

- Fixed Complexity Sphere Decoder providing fixed throughput

- Achieves close-to ML BER performance

- MATLAB and C model for – MIMO 2×2 and 4×4 – Can be modified to support other MIMO sizes – BPSK, 4-QAM, 16-QAM and 64-QAM

- Efficient and optimized FPGA Architecture (4×4 MIMO, 16-QAM)

-

-

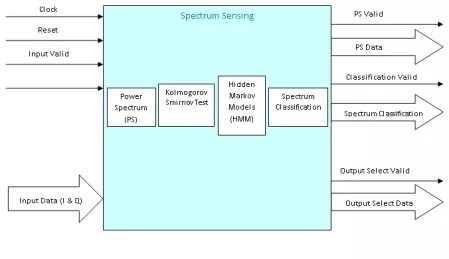

Cognitive Radio IP Core

- Parameterisable Input bit width

- Parameterisable FFT size

- Parameterisable HMM window length

-

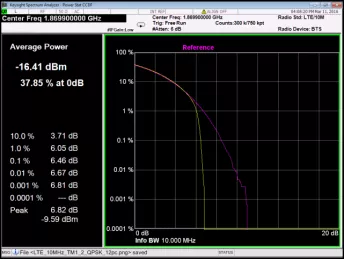

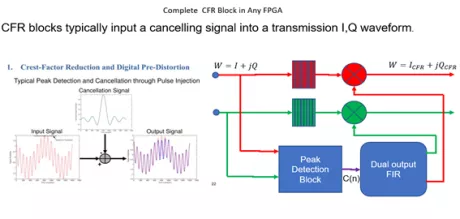

Crest Factor Reduction

- Reduces amplifier costs by enabling the use of power transistors with lower peak-power handling.