Floating-Point Multiplier IP

Welcome to the ultimate Floating-Point Multiplier IP hub! Explore our vast directory of Floating-Point Multiplier IP

All offers in

Floating-Point Multiplier IP

Filter

Compare

10

Floating-Point Multiplier IP

from 5 vendors

(1

-

10)

-

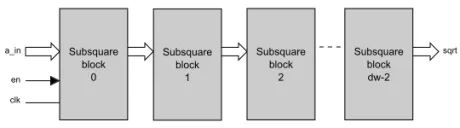

Pipelined Square Root

- Function f(x) = √x

- Input values as unsigned integers

- Output values as unsigned integers

- N-bit value -> n/2 integer bits, n/2 fraction bits

-

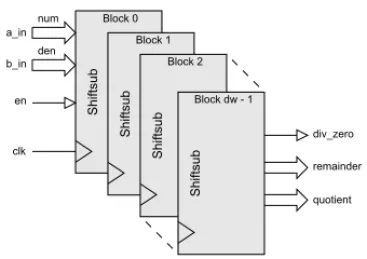

Pipelined Divider

- Function y = a / b

- Input values as signed or unsigned integers

- Output values as signed or unsigned integers

- Configurable dividend and divisor width

-

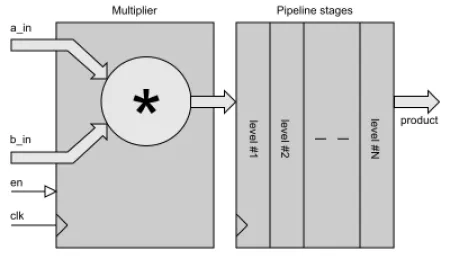

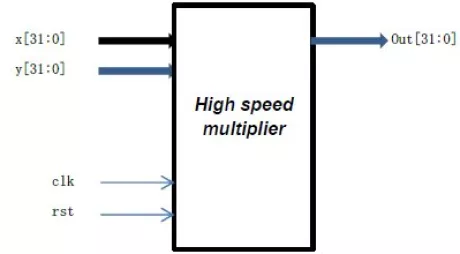

Pipelined Multiplier

- Function y = a * b

- Input values as signed or unsigned numbers

- Output values as signed or unsigned numbers

- Configurable data width and pipeline depth

-

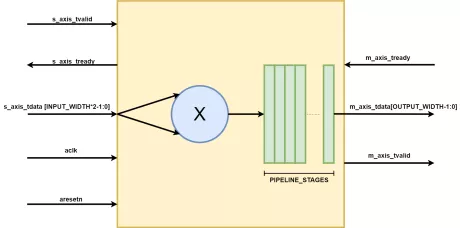

Parameterizable pipelined multiplier

- Synthesizeable, technology-independent IP Core for FPGA/ASIC and SoC

- Coded with SystemVerilog

- Wrapped with AXI Stream interface

- 16-bit Fixed-Point Representation/Operation

- Suitable for DSP or Machine Learning Applications

-

Single precision floating-point 2 cycle's multiplier

- Synthesizable, technology independent Verilog HDL Core.

- 32 bits floating-point arithmetic.

- IEEE 754 compliant

-

Half precision, IEEE 754, floating point fused multiply add

- Half-precision (16-bit) floating point fused multiply and add.

- IEEE 754 compliant.

- Full support for infinities, NaNs and denormals.

- Rounding is to the nearest even number.

-

Single precision, IEEE 754, floating point multiplier

- Single-precision (32-bit) floating point multiplication.

- IEEE 754 compliant.

- Full support for infinities, NaNs and denormals.

- Rounding is to the nearest even number.

-

Multiply Accumulator

- Supports multiplier inputs ranging from 1 to 31 bits unsigned or 2 to 32 bits signed and an output width ranging from 1 to 79 bits unsigned or 2 to 80 bits signed

- Latency can be set for optimal speed or the minimal amount of pipelining allowed "Latency = 1" (accumulation register required)

- Instantaneous Resource Estimation

- For use with Xilinx CORE Generator™

-

Multiplier Accumulator

- Parallel multiply accumulator module.

- Signed or Unsigned inputs parameterizable up to 32-bits.

- Automatic optimization for speed.

- Parameterizable rounding modes or output.

-

Multiplier

- 2's complement signed/unsigned fixed point multiplier

- Parallel and fixed constant coefficient multipliers

- Supports Inputs ranging 1 to 64 bits wide and outputs ranging from 1 to 128 bits wide with any portion of the full product selectable

- Supports symmetric rounding to infinity when using the DSP Slice