USB 3.0 IP

Welcome to the ultimate USB 3.0 IP hub! Explore our vast directory of USB 3.0 IP

All offers in

USB 3.0 IP

Filter

Compare

178

USB 3.0 IP

from 24 vendors

(1

-

10)

-

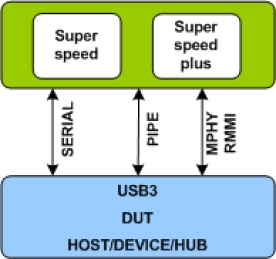

USB 3.0/3.1/3.2/SSIC Verification IP

- Compliant with USB 3.0/3.1/3.2 specification version 1.0

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1 , USB 3.2 and 3.0 OTG

- Complete solution for thorough chip-level verification

- Comprehensive model support a Host, Device, Hub, PHY

-

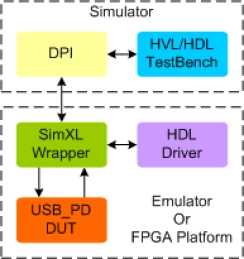

USB PD Synthesizable Transactor

- USB PD Features

- Supports USB Power Delivery Specification 3.1,3.0, 2.0 and 1.0

- Supports USB Type-C Cable and Connector Specification

- Supports Cable plug communication

-

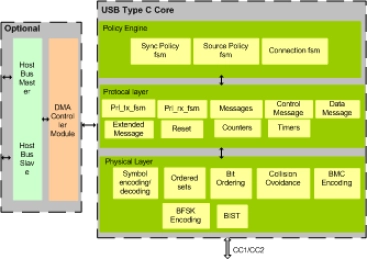

USB TYPE C IIP

- Compliant with USB Type-C Cable and Connector Specification 3.0/2.0 and 1.0

- Supports Debug accessory operation

- Supports Audio accessory operation

- Supports Plug Orientation/Cable Twist Detection

-

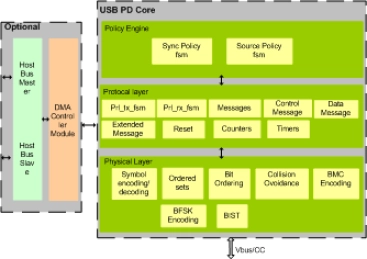

USB PD IIP

- Compliant with USB Power Delivery Specification 3.1/3.0/2.0 and 1.0

- Supports Cable plug communication

- Supports all Resets: Hard, Soft and Cable Resets

- Supports all types of packets.

-

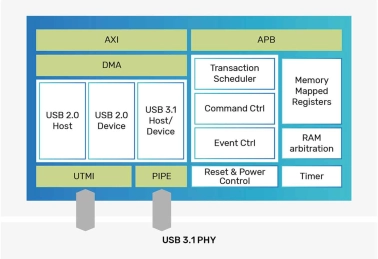

USB 3.x Controller

- Full Link Power Management (U0, U1, U2, and U3) with LFPS support

- Up to 15 IN and 15 OUT configurable endpoints

- Power and clock gating feature support

- Multi-channel Scatter/Gather DMA with TRB caching

- AXI features 128-bit datapath width and 64-bit address width

-

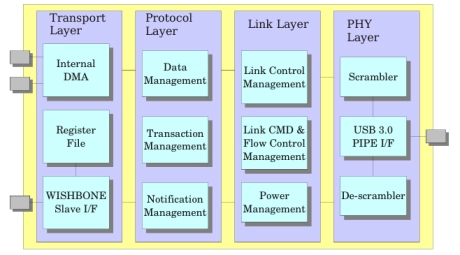

USB 3.0 Device IP Core

- A USB 3.0 Device IP Core that provides high performance SuperSpeed USB connectivity in a small footprint solution for quick and easy implementation of a USB Device interface.

- The USB 3.0 Device IP Core is fully USB 3.0 compliant.

-

SuperSpeed USB 3.0 Host Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Dual Role Device Controller, Configurable for SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Device Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

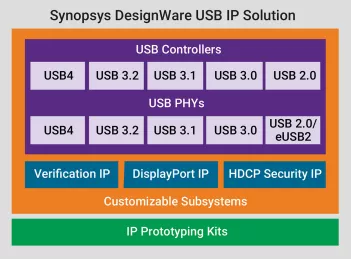

USB-C 3.0 femtoPHY, Type-C - TSMC 28HPC, North/South Poly Orientation

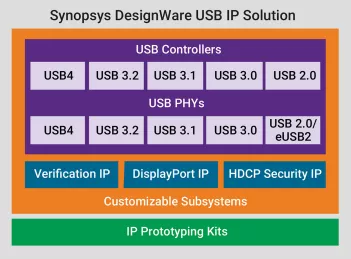

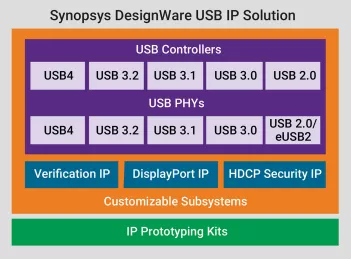

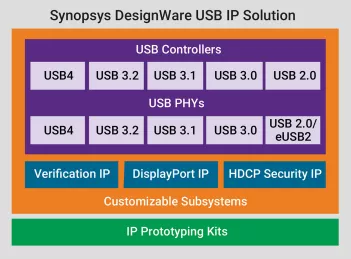

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification