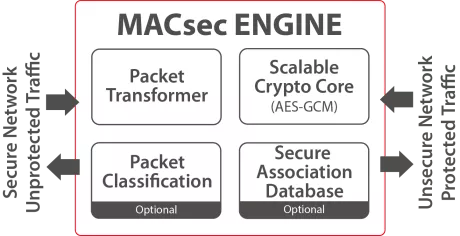

MACsec Engine IP

Welcome to the ultimate MACsec Engine IP hub! Explore our vast directory of MACsec Engine IP

All offers in

MACsec Engine IP

Filter

Compare

25

MACsec Engine IP

from 10 vendors

(1

-

10)

-

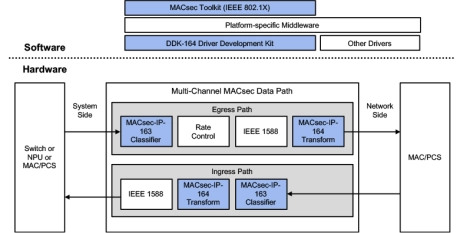

800G Multi-Channel MACsec Engine with TDM Interface

- Complete and fully compliant MACsec Packet Engine with classifier and transformation engines for rates of 100 to 800 Gbps, up to 64 channels, ready for FlexE

- All IEEE MACsec standards supported (including IEEE802.1AE-2018). Optional inclusion of Cisco extensions, IPsec ESP tunnel and transport mode with AES-GCM cipher

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

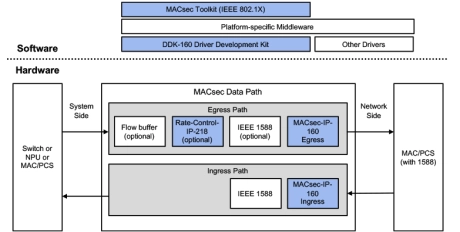

1G to 100G Single-Port MACsec Engine

- Complete HW/SW system.

- Driver Development Kit.

- High-speed MACsec Frame Engine

- Silicon-proven implementation

- Fast and easy to integrate into SoCs.

- Flexible layered design.

-

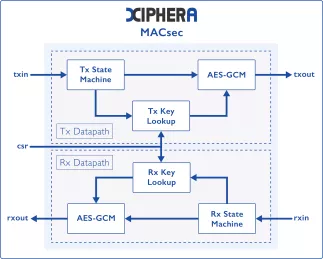

MACsec - Extreme-Speed Variant

- Moderate resource requirements

- Performance

- Standard Compliance

-

Media Access Control Security (MACSec)

- Up to four ports of concurrent traffic with an aggregate bandwidth of 100G are supported by one core (1x100G, 2x50G, 2x40G, 4x25G, 4x10G, 4x1G, 1x50G+2x25G)

- Line rate operation

- Flexible control/non-control port filtering

- Configurable number of Secure Channels (SCs) and Security Associations (SAs) per physical port

-

1.5Tbps MACsec Engine

- Throughput up to 1.5Tb

- ASIC and FPGA

- Multi-channel support for link aggregation or FlexE

-

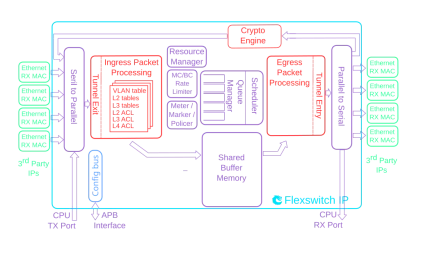

Ethernet IPSec/MACSec Switch/Router IP Core - Efficient and Massively Customizable

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 32733 bytes.

-

MACsec 10G/25G

- Compliance with IEEE Std 802.1AE-2018

- Line-rate traffic encryption and decryption

- Supports 10G/25G data rates

- Multiple Connectivity Associations (SecYs) with Traffic Mapping Rules

-

IEEE 802.1ae (MACsec) Security Processor

- Small size combined with high performance:

- Self-contained, uses two external memories for key storage and statistic counters

- Very low latency

- Back-to-back packet processing

-

P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core

- Small size: From 60K ASIC gates (at throughput of 18.2 bits per clock)

- 487 MHz frequency in 90 nm process

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

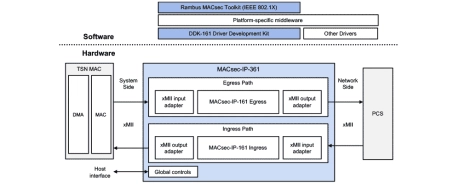

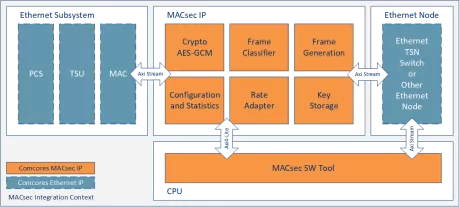

1G to 50G Single-Port MACsec Engine with xMII interface and TSN support

- MACsec solution for integration between MAC and PCS side supporting 1GbE to 50GbE rates with optional TSN support (including IEEE803.2br).

- For MACsec function integrates the MACsec-IP-161 with all IEEE MACsec standards supported. Optional Cisco ClearTags.

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management