HSI IP

Filter

Compare

109

IP

from 13 vendors

(1

-

10)

-

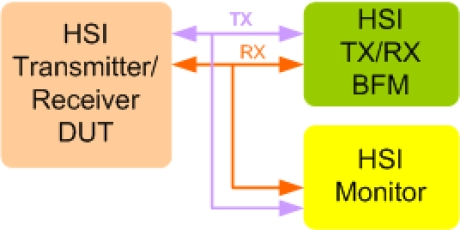

MIPI HSI Verification IP

- Supports 1.01 MIPI HSI Specification.

- Full MIPI HSI Tx and Rx functionality.

- Monitor,Detects and notifies the testbench of all protocol and timing errors.

- Supports data flow

-

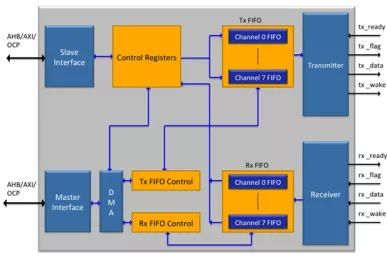

MIPI HSI Controller - (High-Speed Synchronous Serial Interface)

- Compliant with MIPI HSI Specification version 1.0, and Physical Layer version 1.01.00

- Full Duplex High Speed Serial Interface between two peer devices

- 32 bit AHB, AXI or OCP Interface to CPU/Memory sub-system

-

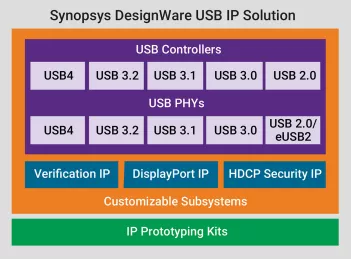

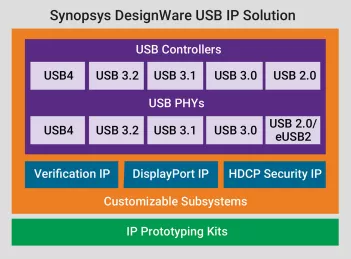

SuperSpeed USB 3.0 Host Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Dual Role Device Controller, Configurable for SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Device Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

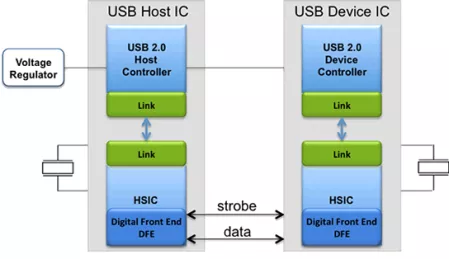

HSIC PHY

- Consumes <90mW during data transfer

- Consumes <50uW when not transferring data

- Uses standard chip digital and IO supplies

- Low pin count

-

USB HSIC PHY - High Speed Inter-Chip IP Core

- High-Speed 480Mbps data rate only

- Source-synchronous seriel interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

-

USB 2.0 Hi-Speed OTG Controller Subsystem w/AHB Interface Supporting HSIC (config. as Device only or Full Speed only)

- Configuration options to maximize performance and minimize CPU interrupts

- Flexible parameters enable easy integration into low and high-latency systems

- Transfer- or transaction-based processing of USB data based on system requirements

- Configurable data buffering options to fine-tune performance/ area trade-offs

-

HW/SW interface foundation for design innovation

- Various Input Formats:

- CSRSpec Language

- SystemRDL

- IP-XACT

-

IEEE 802.15.3c (60 GHz PHY) Multi-Gbit/s LDPC Decoder

- Compliant with IEEE 802.15.3c-2009 standard

- Suitable for single carrier (SC) mode and high speed interface (HSI) mode.

- Support for all short LDPC codes (672 bits, code rates 1/2, 5/8, 3/4, 7/8)