LPDDR2 IP

Welcome to the ultimate LPDDR2 IP hub! Explore our vast directory of LPDDR2 IP

All offers in

LPDDR2 IP

Filter

Compare

9

LPDDR2 IP

from 3 vendors

(1

-

9)

-

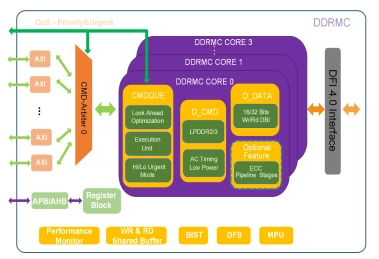

Universal Multiport Memory Controller - LPDDR 3/2 Controller

- Compliant with AXI V4.0 specification

- Compliant with DFI 3.1 specification

- Compliant with JEDEC LPDDR2 and LPDDR3 standards

- Support for 8, 16, 32 SDRAM bus width, for a total memory data path width up to 64 bits

-

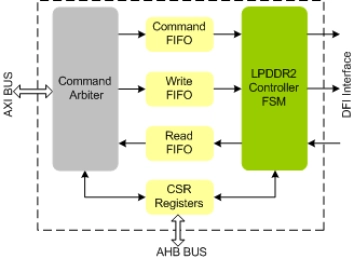

LPDDR2 IP solution

- Compatible with LPDDR2 up to 1066Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

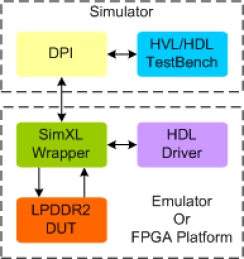

LPDDR2 Synthesizable Transactor

- Supports 100% of LPDDR2 protocol standard JESD209-2E and JESD209-2F

- Supports all the LPDDR2 commands as per the specs

- Supports up to 32GB device density

- Supports following devices:

-

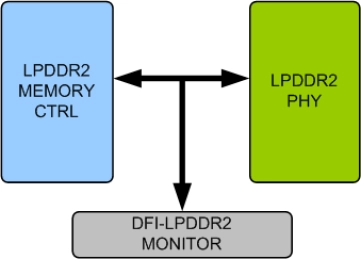

LPDDR2 DFI Verification IP

- Compliant with DFI version 2.1 or higher Specifications.

- Supports LPDDR2 devices compliant with JEDEC LPDDR2 SDRAM Standard JESD209-2F.pdf and JESD209-2E.pdf

- Supports for Read data-eye training

- Supports for Read gate training

-

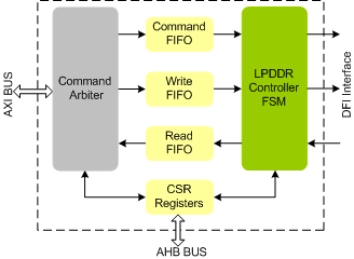

LPDDR2 Controller IIP

- Supports LPDDR2 protocol standard JESD209-2E and JESD209-2F Specification

- Compliant with DFI version 2.1 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

LPDDR Controller IIP

- Supports LPDDR protocol standard and JESD209A-1 and JESD209B Specification

- Compliant with DFI version 2.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transcations for AXI write and read channels

-

LPDDR DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf.

- Supports all Interface Groups.

-

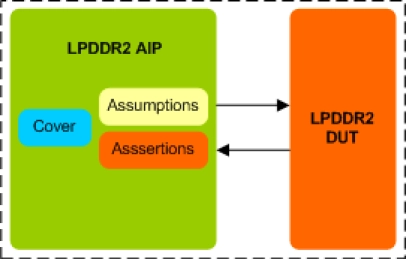

LPDDR2 Assertion IP

- Specification Compliance

- Supports LPDDR2 memory devices from all leading vendors.

- Supports 100% of LPDDR2 protocol standard JESD209-2E and JESD209-2F.

- Supports all the LPDDR2 commands as per the specs.

-

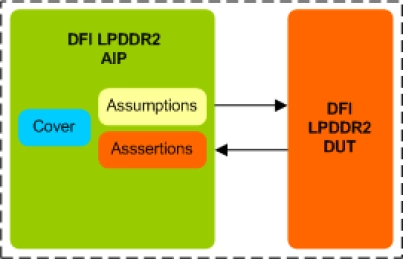

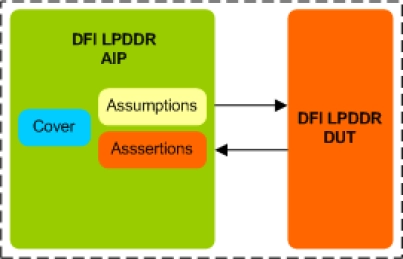

LPDDR2 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.1 or higher Specifications.

- Supports LPDDR2 devices compliant with JEDEC LPDDR2 SDRAM Standard JESD209-2F.pdf and JESD209-2E.pdf.

- Supports for Read data-eye training.