USB 3.2 PHY IP

Welcome to the ultimate USB 3.2 PHY IP hub! Explore our vast directory of USB 3.2 PHY IP

All offers in

USB 3.2 PHY IP

Filter

Compare

12

USB 3.2 PHY IP

from 4 vendors

(1

-

10)

-

eUSB2 Repeater

- Designed for mature process nodes, such as 28nm

- Supports the USB 2.0 protocol and High Speed, Full Speed, and Low Speed data rates

- eUSB2 Repeater converts between eUSB2 and USB 2.0 signaling levels

- eUSB2 Repeater enables an SoC design with eUSB2 PHY IP to connect to legacy USB 2.0 products

-

USB3.2 Gen2 x2-lane, Dual-Role PHY, TSMC N6, 1.8V, N/S orientation, type-C

- Worldwide smallest USB 3.2 Gen2 PHY IP (e.g. IP size @28HPC+ is smaller than 0.7mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2 and 2.0 electrical specifications

- Supports clock inputs from 10/12/19.2/24/25/27/30/40MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

-

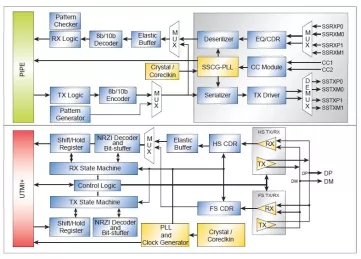

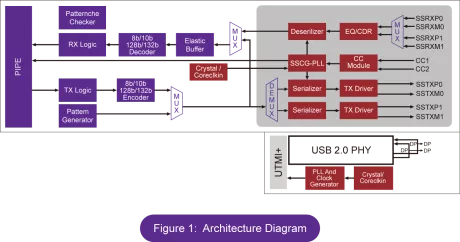

USB 3.2 Gen2x2 with PIPE 4.3 and USB2.0 with UTMI+ interface

- Fully compliant with USB 3.2 Gen2x1 featuring PIPE 4.3 and USB 2.0 with a UTMI+ interface

- Supports host, peripheral, and dual-role applications

- Supports 10/12/25/30/19.2/24/27/40 MHz crystal oscillators or clock inputs

- Supports TX 3-Tap FFE and RX CTLE+1-Tap DFE for SS+

-

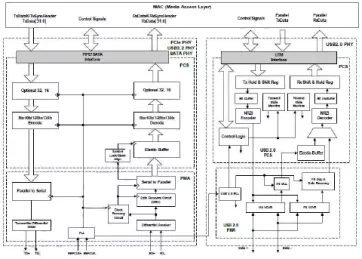

USB 3.2/ PCIe 3.1/ SATA 3.2 Combo PHY IP, Silicon Proven in UMC 28HPC

- Compliant with PCIe 3.1 Base Specification

- Compliant with Universal Serial Bus 3.2 Specification

- Compliant with Universal Serial Bus 2.0 Specification

- Compliant with UTMI 1.05 Specification

-

USB-C 3.2 SS/SSP PHY in Type-C in TSMC (N7, N6, N5, N3E)

- Supports 20Gbps, 10Gbps, and 5Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

-

USB-C 3.2 SS/SSP PHY in Type-C in Samsung (SF4X, SF4E, SF2)

- Supports 20Gbps, 10Gbps, and 5Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power