Security Protocol Engine IP for TSMC

Welcome to the ultimate Security Protocol Engine IP for TSMC hub! Explore our vast directory of Security Protocol Engine IP for TSMC

All offers in

Security Protocol Engine IP

for TSMC

Filter

Compare

6

Security Protocol Engine IP

for TSMC

from 2 vendors

(1

-

6)

-

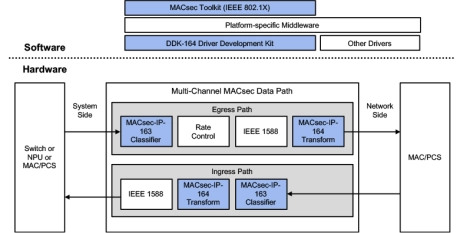

800G Multi-Channel MACsec Engine with TDM Interface

- Complete and fully compliant MACsec Packet Engine with classifier and transformation engines for rates of 100 to 800 Gbps, up to 64 channels, ready for FlexE

- All IEEE MACsec standards supported (including IEEE802.1AE-2018). Optional inclusion of Cisco extensions, IPsec ESP tunnel and transport mode with AES-GCM cipher

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

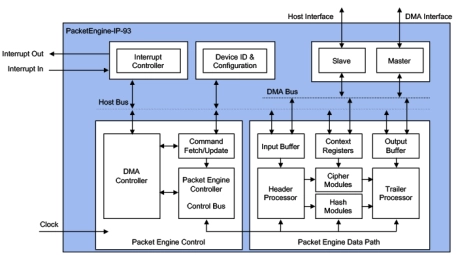

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto

-

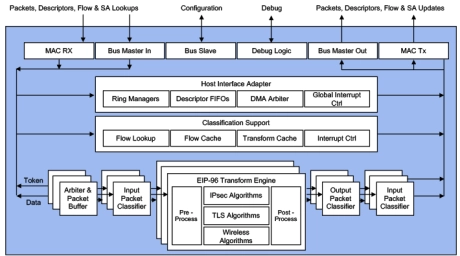

Multi-Protocol Engine with Classifier, Inline and Look-Aside, 10-100 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP, MACsec packet engine with classifier and in-line interface for multi-core server processors

- 10-100 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, streaming and AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP.

-

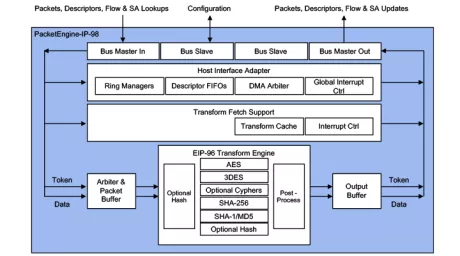

Multi-Protocol Engine, Look-Aside, 1 Gbps

- Protocol-aware IPsec/TLS packet engine with Look-Aside interface for IoT.

- Up to 1 Gbps, lowest gate count in the industry, just 100K gates (ex AMBA interface).

- Supported by Driver Development Kit, QuickSec IPsec toolkit, Secure Boot Toolkit.

-

MACsec 10G/25G

- Compliance with IEEE Std 802.1AE-2018

- Line-rate traffic encryption and decryption

- Supports 10G/25G data rates

- Multiple Connectivity Associations (SecYs) with Traffic Mapping Rules

-

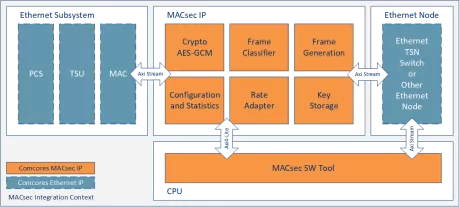

1G to 50G Single-Port MACsec Engine with TSN support

- Complete and compliant MACsec Packet Engine for rates from 1GbE to 50GbE with TSN support (including IEEE803.2br).

- All IEEE MACsec standards supported (incl. IEEE802.1AE-2018). Optional Cisco ClearTags.

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management