Crypto Accelerator IP for TSMC

Welcome to the ultimate Crypto Accelerator IP for TSMC hub! Explore our vast directory of Crypto Accelerator IP for TSMC

All offers in

Crypto Accelerator IP

for TSMC

Filter

Compare

20

Crypto Accelerator IP

for TSMC

from 1 vendors

(1

-

10)

Filter:

- 7nm

-

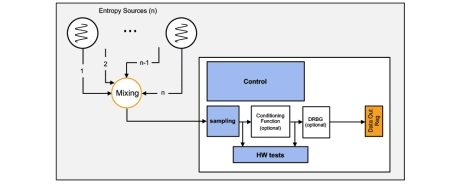

NIST ESV certified, AIS-31, FIPS (SP800-90A/B/C) True Random Number Generator

- Non-deterministic Random Number Generator, FIPS-140 SP800-90A/B compliant, ESV certified for NRBGs and DRBGs (#E167).

- High performance, low power, fully digital, standard cell only, supports all CMOS nodes.

- Available as standalone RBG or embedded in the Rambus RT-130, RT-630, RT-660 Root of Trusts

-

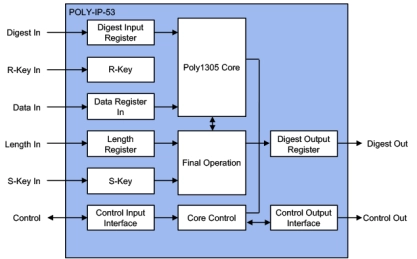

Poly1305 Crypto Accelerator

- Wide bus interface (128-bit data, 128-bit keys, 135-bit digest) or 32-bit register interface

- Key size: 128 bits

- Includes initialization stage

- Supports continuation mode

- Fully synchronous design

-

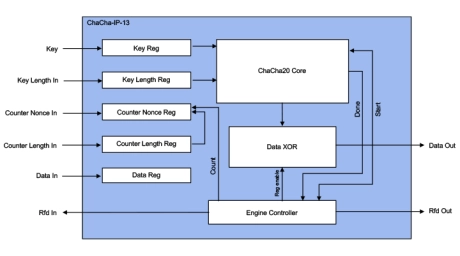

ChaCha20 Accelerators

- Wide bus interface (512-bit data, 256-bit keys) or 32-bit register interface

- Key sizes: 128 and 256 bits

- Includes key scheduling hardware

- Feedback mode CTR.

-

High speed low latency AES-GCM pipeline, 100Gbps

- Silicon-proven implementation

- Fast and easy to integrate into SoCs

- Flexible layered design

- World-class technical support

-

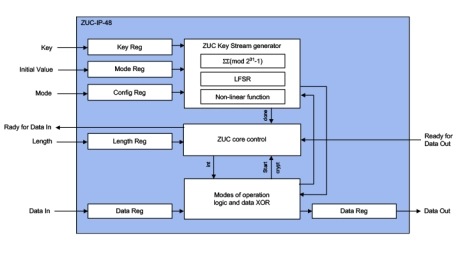

3GPP ZUC Accelerators

- Wide bus interface (32-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware

- Supported modes: 128-EEA3 and 128-EIA3

- Fully synchronous design

- Low Speed, High Speed versions

-

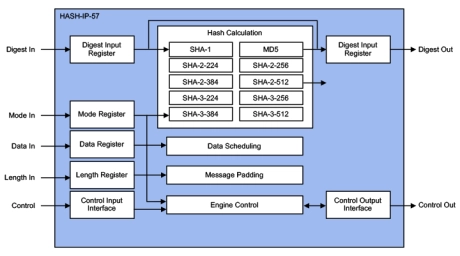

SHA-3, SHA-2, SHA-1, SM3, MD5, Hash Accelerators

- Wide bus interface (1024-bit data, 512-bit digest) or 32 bit register interface

- MD5, SHA-1, SHA-2, SHA-3

- SHA-2/3 in 224/256/384/512 modes

- Message puffing for all algorithms

- Message data scheduling hardware

-

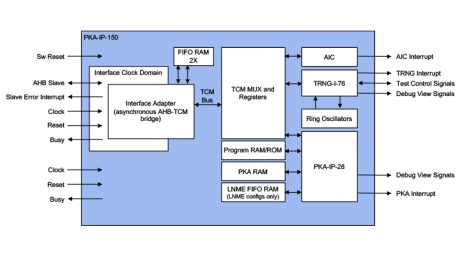

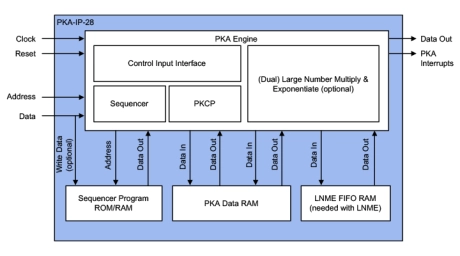

RSA/ECC Public Key Accelerators with TRNG and AHB

- Up to 4160-bit modulus size for RSA & 768-bit modulus for prime field ECC operations

- Public key signature generation, verification and key negotiation with little involvement of host

- NIST CAVP compliant for FIPS 140-3

-

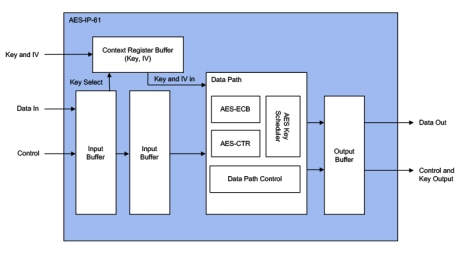

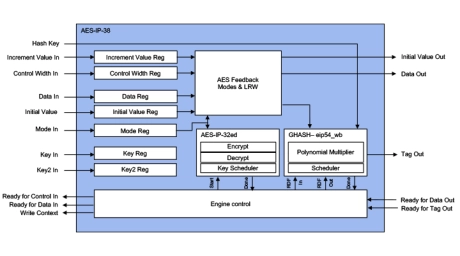

AES XTS/GCM Accelerators

- Wide bus interface

- Basic AES encrypt and decrypt operations

- Key sizes: 128, 192 and 256 bits

- Key scheduling in hardware, allowing key, key size and direction changes every 13/15/17 clocks with zero impact on throughput

- Hardware reverse (decrypt) key generation

-

Small RSA/ECC Public Key Accelerators

- Up to 4160-bit modulus size for RSA & 768-bit modulus for prime field ECC operations

- Public key signature generation, verification and key negotiation with little involvement of host

- NIST CAVP compliant for FIPS 140-3

-

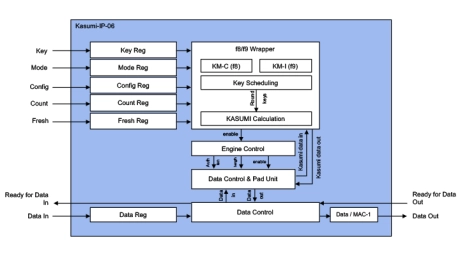

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.