Poly1305 Crypto Accelerator

Poly-IP-53 (EIP-53) is IP for accelerating the Poly1305 hash-based message authentication algorithm (RFC7539), supporting the NIS…

Overview

Poly-IP-53 (EIP-53) is IP for accelerating the Poly1305 hash-based message authentication algorithm (RFC7539), supporting the NIST MAC mode up to 6.4 Gbps @ 450MHz. Designed for fast integration, low gate count and full transforms, the Poly-IP-53 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed crypto pipelines.

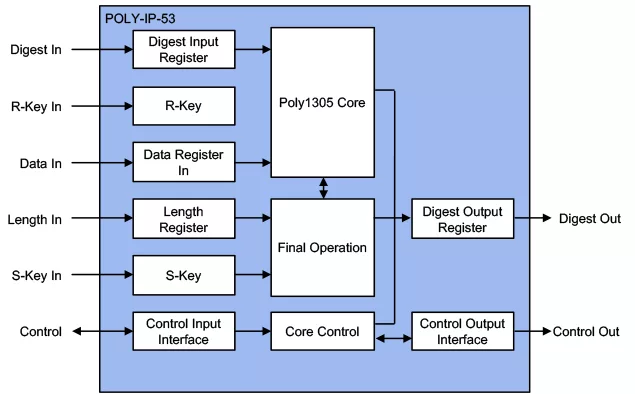

How the POLY-IP-53 works

The Poly-IP-53 is a family of the cryptographic library elements in the Rambus hardware IP library (formerly of Inside Secure). For example, the Poly-IP-53 is the cipher core embedded in the Vault-IP-140 platform security engines providing support for TLS1.3 and HomeKit IoT applications (Poly1305 is also available as software implementation in the VaultIP core). The accelerators include I/O registers, encryption and decryption cores, and the logic for feedback modes and key scheduling.

Sustained performance for any object sizes ranges from 1 to 6.4 Gbps depending on the configuration and area. Gate count is around 50K gates depending on the configuration.

Key features

- Wide bus interface (128-bit data, 128-bit keys, 135-bit digest) or 32-bit register interface

- Key size: 128 bits

- Includes initialization stage

- Supports continuation mode

- Fully synchronous design

Block Diagram

Benefits

- Silicon-proven implementation

- Fast and easy to integrate into SoCs

- Flexible layered design

- Complete range of configurations

- World-class technical support

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Symmetric Crypto IP core

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Google, Quantum Attacks, and ECDSA: Why There’s No Need to Panic and Why Preparation Matters Now

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Frequently asked questions about Symmetric Cryptography IP cores

What is Poly1305 Crypto Accelerator?

Poly1305 Crypto Accelerator is a Symmetric Crypto IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.