DDR IP for GLOBALFOUNDRIES

Welcome to the ultimate DDR IP for GLOBALFOUNDRIES hub! Explore our vast directory of DDR IP for GLOBALFOUNDRIES

All offers in

DDR IP

for GLOBALFOUNDRIES

Filter

Compare

19

DDR IP

for GLOBALFOUNDRIES

from 4 vendors

(1

-

10)

-

DDR PHY

- DDR5/4/3 training with write-leveling and data-eye training

- Optional clock gating available for low-power control

- Internal and external datapath loop-back modes

- I/O pads with impedance calibration logic and data retention capability

- Programmable per-bit (PVT compensated) deskew on read and write datapaths

- RX and TX equalization for heavily loaded systems

-

DDR5/4 PHY - GF 12LP+

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

LPDDR4X multiPHY Plus in GF (12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4X multiPHY in GF (14nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in GF (22nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in GF (22nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

DDR5/4 PHY in GF (12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR5 SDRAMs up to 8400 Mbps

- Compatible with JEDEC standard DDR4 SDRAMs up to 3200 Mbps

- DFI 5.0 compliant interface to the memory controller

-

PSRAM PHY

- PSRAM modes & signaling, rates from 200Mbps up to 1600Mbps

- x8 data path interface

- 2.5V I/O devices

- Multiple drive strengths adjustable

-

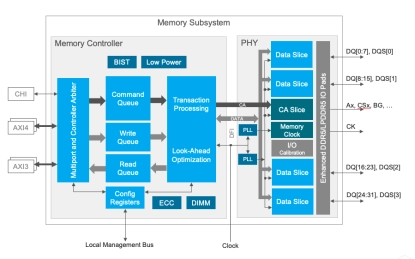

DDR5/4 Combo PHY & Controller

- DDR5 and DDR4 modes & signaling, rates from 20Mbps up to 5200Mbps (DDR5) and 3200Mbps (DDR4), respectively

- x16/x32/x64/x72/x80 data path interface extendable, support UDIMM, RDIMM and LRDIMM

- 1.1V/1.2V JEDEC IO standard, supporting 1.1V POD_11 and 1.2V POD_12 I/Os

- Support DDR5 dual channel mode, dual 32bit data +8bit ECC

-

DDR3/3L/2/LPDDR3/2 Combo PHY & Controller

- LPDDR3/2 modes & signaling, rates from 20Mbps up to 2133Mbps (DDR3/3L), 1066Mbps (DDR2/LPDDR2) and 1600Mbps (LPDDR3) respectively

- x16/x32/x64 data path interface extendable

- 1.2V/1.35V/1.5V/1.8V JEDEC IO standard, support 1.2V POD_12 and 1.35V/1.5V/1.8V SSTL I/Os

- Multiple drive strengths adjustable