In production since 2018.

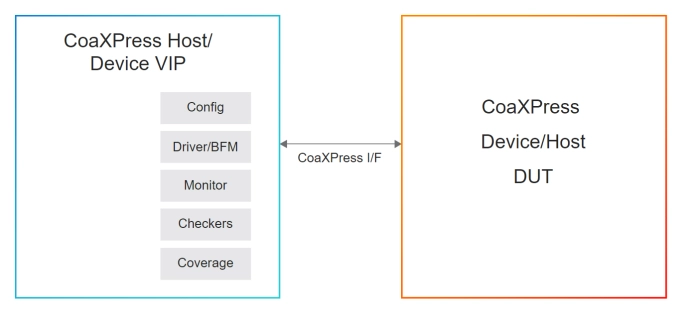

This Cadence® Verification IP (VIP) supports the CoaXPress standard. It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for CoaXPress is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: The VIP for CoaXPress supports the specification versions: 1.0, 1.1, and 1.1.1.