Key attributes of the GlobalFoundries 65nm IO library are dual selectable drive strengths and independent input & output enable / disable. The GPIO cell can be configured as input, output or open-drain with a Schmitt trigger input and selectable internal 60K ohm pull-up or pull-down resistor. ESD protection for IO and core supplies is constructed in an aggressive footprint. 2.5V LVDS RX & TX cells capable of data rates up to 1.5Gbps (with no external reference) and a 2.5V low-capacitance analog/RF cell complement the GPIO offering. The library is enriched with filler, corner and domain-break cells to allow for flexible pad ring construction.

Built into our IO libraries, and also offered as a separate service, is our strong ESD expertise. Certus was founded by ESD engineers and our results speak for themselves. Not only do we consistently exceed the standard ESD targets of 2KV HBM and 500V CDM, but we also provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD and Cable Discharge Events (CDE).

Certus supports additional IO libraries in GlobalFoundries technologies, as well as at TSMC and Samsung. Certus is particularly suited at providing custom variants in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

A 65nm Wirebond IO library with 2.5V GPIO, LVDS TX & RX and 2.5V analog / RF

Overview

Key Features

- GPIO:

- 2.5V nominal IO operation

- Selectable 12mA | 24mA drive strength options

- Up to 200MHz operation (@24mA, 10pF)

- Output enable (HiZ when disabled)

- Input enable (input low when disabled)

- Schmitt trigger receiver

- 60K? selectable pull-up or pull-down resistor

- ESD: 2KV HBM, 500V CDM2

- Silicon proven

- LVDS TX & RX

- 2.5V nominal operation

- Data rates of 1.5Gbps

- Output / Input enable

- Built-in 100? RX termination resistor

- Fault-safe mode for shorted or open RX pins

- Internally generated common mode reference (no external pin required)

- Power-on sequence independence

- ESD protection of 2KV HBM, 500V CDM

- ANALOG / RF

- 2.5V tolerant

- Low capacitance

- 2KV HBM, 500V CDM

- Physical Attributes

- 8-metal stack - B1_EA

- 45um x 200um cell size

- 45um dual row wirebond pitch

Benefits

- Selectable drive strengths

- Independent input & output enable

- Up to 200MHz operation

- Customizable

- Pull-up / pull-down resistor options

- ANSI TIA/EIA-644-A compliant 2.5V LVDS RX & TX

- Low-capacitance analog / RF cell

- 45um dual row wirebond pitch

- Silicon proven

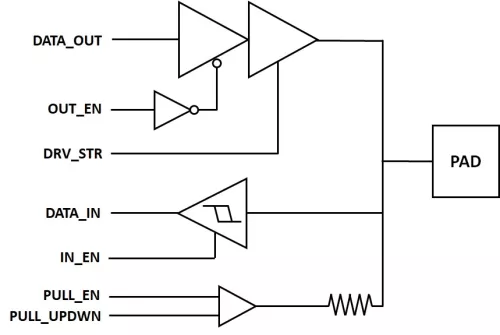

Block Diagram

Applications

- LVCMOS GPIO, LVDS, RF/Analog

Deliverables

- GDS

- CDL netlist

- Verilog stub

- Verilog behavioral model

- LEF

- Liberty Timing Files

- IBIS (option)

- Electrical datasheet

- User guide and application notes

- Consulting and Support

Technical Specifications

Foundry, Node

GlobalFoundries 65nm LPe

Maturity

Silicon-Proven

Availability

Immediate

GLOBALFOUNDRIES

In Production:

65nm

LPe

Pre-Silicon: 65nm LPe

Silicon Proven: 65nm LPe

Pre-Silicon: 65nm LPe

Silicon Proven: 65nm LPe

Related IPs

- 28nm Wirebond IO library with dynamically switchable 1.8V/ 3.3V GPIO, 5V I2C open-drain, 1.8V & 3.3V analog, OTP program cell, and HDMI & LVDS protection macros - featured across a variety of metal stack and pad configuration options

- A 65nm Wirebond IO library with 1-3.3V GPIO, 3.3V pulse-width modulation cell, I2C & SVID open-drain, 3.3V & 5V analog and OTP program cell

- A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell

- GlobalFoundries 0.13um 2.5v IO Library

- The GF28SLPV25_ADC_13 IP is a 2.5V 12Bit pipeline analog to digital converter capable of running at up to 100MHz conversion rate with 2Vp-p input range.

- The GF55LPEV25_ADC_13 IP is a 2.5V 12Bit pipeline analog to digital converter capable of running at up to 100MHz conversion rate with 2Vp-p input range.