Quantum Safe Crypto Accelerator IP

Welcome to the ultimate Quantum Safe Crypto Accelerator IP hub! Explore our vast directory of Quantum Safe Crypto Accelerator IP cores.

Quantum Safe IP cores offer a hardware-level security solution to protect data and hardware against quantum computer attacks using NIST and CNSA selected algorithms.

All offers in

Quantum Safe Crypto Accelerator IP

Filter

Compare

22

Quantum Safe Crypto Accelerator IP

from 11 vendors

(1

-

10)

-

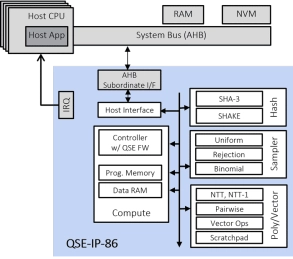

Fast Quantum Safe Engine for ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) with DPA

- Compliant with FIPS 203 ML-KEM and FIPS 204 ML-DSA standards

- Uses CRYSTALS-Kyber, CRYSTALS-Dilithium quantum-resistant algorithms

- Includes SHA-3, SHAKE-128 and SHAKE-256 acceleration

- The embedded QSE CPU combined with Rambus-supplied firmware implements the full FIPS 203/204 protocols

-

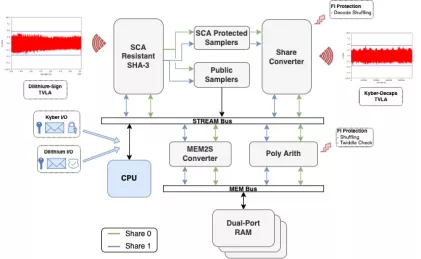

Unified Hardware IP for Post-Quantum Cryptography based on Kyber and Dilithium

- Turn-key implementations of the NIST FIPS recommended CRYSTALS post-quantum for key encapsulation (KEM) and digital signature algorithm (DSA)

-

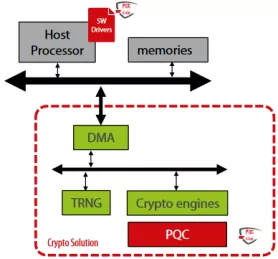

Secure-IC's Securyzr Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

- Scalable architecture and crypto engines for optimal performance/resource usage

- Configurable for perfect application fit

- 100% CPU offload with low latency and high throughput

- DPA countermeasures Full software/driver support

-

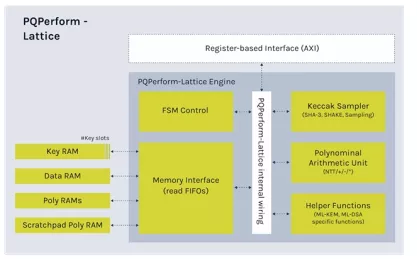

High-speed, high-throughput, lattice PQC cryptographic subsystem

- A powerful hardware-based product that is designed for high throughput and high speed.

- PQPerform-Lattice adds post-quantum cryptography for applications that handle a large number of transactions, such as high-capacity network hardware applications or HSMs (hardware security modules) requiring fast performance.

- It’s designed for performance and supports FIPS 204 ML-DSA digital signatures for quantum-secure authentication and FIPS 203 ML-KEM for quantum-secure key exchange.

-

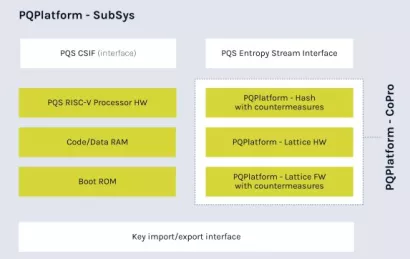

Self-contained cryptographic subsystem designed for PQC + classical, minimal integration effort, with SCA protection

- A cryptographic subsystem, designed to provide cryptographic services.

- These services include post-quantum signature generation, verification, and secure key establishment.

- PQPlatform-SubSys uses its built-in CPU independently from the surrounding system, allowing cryptographic services to be offloaded efficiently from the system processor.

-

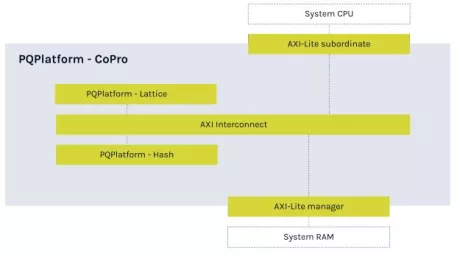

Post-Quantum Cryptography Processor

- PQPlatform-CoPro (PQP-HW-COP) adds PQShield’s state-of-the-art post-quantum cryptography (PQC) to your security sub-system, with optional side-channel countermeasures (SCA).

- PQPlatform-CoPro can be optimized for minimum area as part of an existing security sub-system.

- PQPlatform-CoPro is designed to be run by an existing CPU in your security system, using PQShield’s supplied firmware.

-

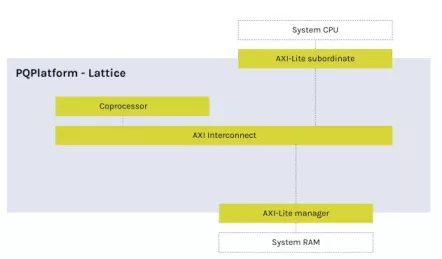

Lattice-based Post-Quantum Cryptography Processing Engine

- PQC(post-quantumcryptography) engine

- NISTSP800-56Acomplaint

- NISTFIPS186-4and186-5compliant

- ANSSIX9.142-2020compliant

-

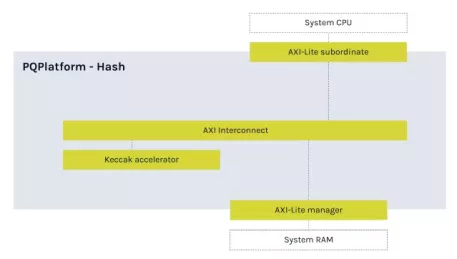

Hash-based post-quantum hardware accelerator

- Power side-channel secure (SCA) Keccak engine

- AXI4-Lite (64-bit 1x subordinate)

- NIST FIPS-202 SHA3-224/256/384/512

-

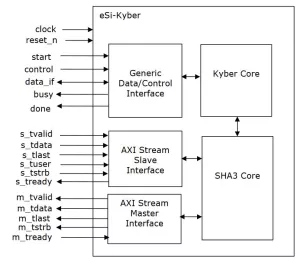

CRYSTALS Kyber core for accelerating NIST FIPS 203 Key Encapsulation Mechanism

- Designed to accelerate post-quantum Key Encapsulation Mechanism (KEM) as defined by NIST FIPS 203.

-

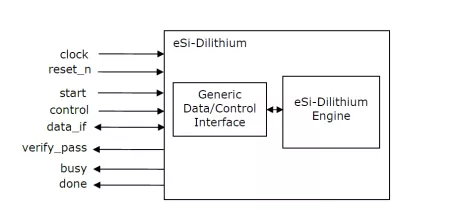

CRYSTALS Dilithium core for accelerating NIST FIPS 204 Module Lattice Digital Signature algorithm

Hardware core for accelerating the high-level operations specified in the NIST FIPS 204 standard.