MIPI I3C V1.1 IP

Filter

Compare

23

IP

from 9 vendors

(1

-

10)

-

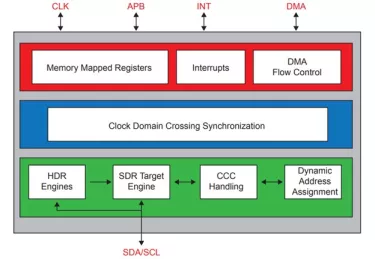

MIPI I3C Slave v1.1 Controller IP enables efficient data flow for sensor integration.

- Compliant with the MIPI Alliance Specification for I3C Version 1.0

- Supports modes of Master – SDR [12.5 MHz], HDR DDR and HDR- Ternary (TSP, TSL) Modes

- Supports IBI, Hot Join

- Dynamic Addressing assignment support

-

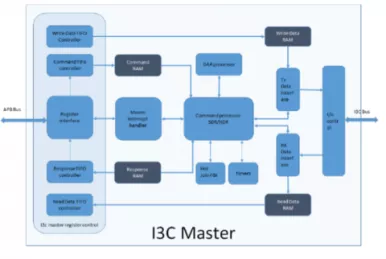

MIPI I3C Master v1.1 Controller IP offers impressive data transmission capacity for sensor integration.

- Compliant with the MIPI Alliance Draft Specification for I3C Version 0.5 Revision 1.0

- Supports all modes of Master – SDR [12.5 MHz], HDR and HDR-DDR, I2C Modes.

- Supports interrupt handling.

- Enables peer to peer communication.

-

MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- Conforms to MIPI I3C v1.1 specifications

- MIPI Manufacturer ID: 0x03B3

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices

- Legacy I2C messaging

-

MIPI I3C v1.1.1 Controller and Target

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps

-

MIPI I3C v1.1.1 Basic Target lite

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps

-

MIPI I3C v1.1.1 Basic Controller and Target

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps

-

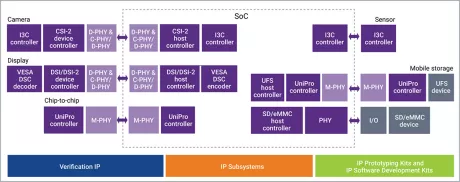

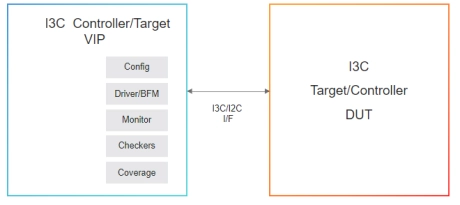

Simulation VIP for MIPI I3C

- I3C SDR Mode

- SDR private read/write data transfers

- I3C HDR-DDR Mode

- HDR-DDR enter and exit patterns, command coding, bus turnaround, DDR Flow Control Elements and error detection

-

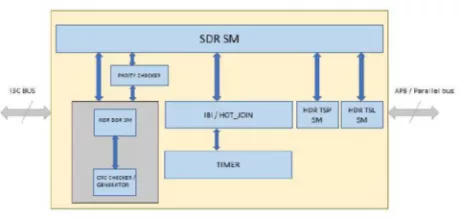

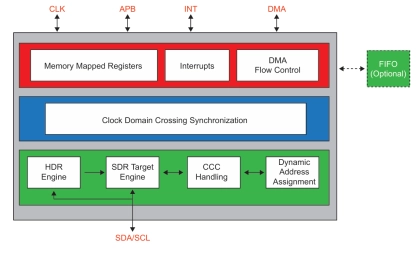

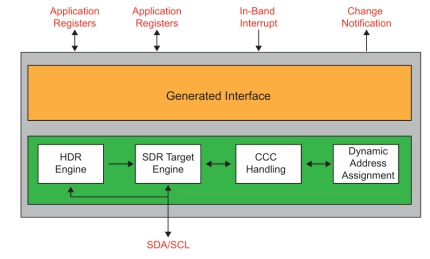

I3C V1.1 Advanced Target

- The I3C Advanced Target is a highly configurable I3C Target that can be used in microcontroller based environments to provide I3C connectivity to any device.

- It can be configured in a number of different ways to allow the core to use the minimum amount of logic to reduce both area (cost) and power.

-

I3C V1.1 Autonomous Target

- The I3C Autonomous Target is intended for simple, data acquisition types of applications where a microprocessor is not needed to process the data.

- Instead, data is exchanged via a simple set of register interfaces to the application and the controller autonomously manages all of the communication to an upstream I3C Controller.

-

I3C V1.1 Advanced Controller

- The I3C Advanced Controller is a highly configurable I3C controller that can be used in microcontroller-based environments to provide I3C connectivity to any device.

- It contains controller capabilities as well as many of the same features as the I3C Advanced Target.