LLI IP

Filter

Compare

17

IP

from 8 vendors

(1

-

10)

-

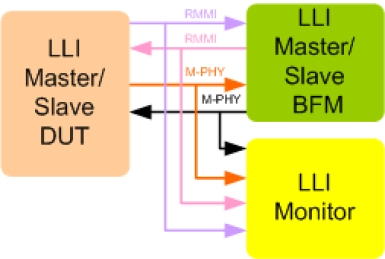

MIPI LLI Verification IP

- Supports MIPI LLI specification 1.0.

- Support MIPI MPHY Type-I specification

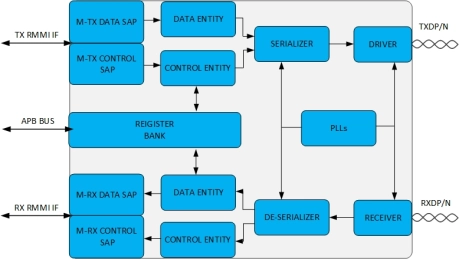

- PHY layer supports MPHY serial, MPHY RMMI (10,20,40 bit) Interface

- PHY layer supports multi lanes, Type-I and all power modes for Mphy

-

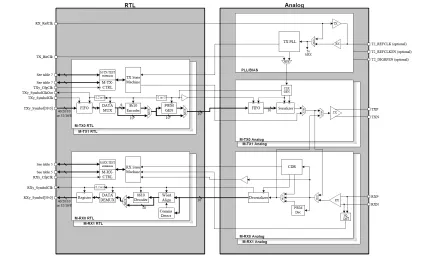

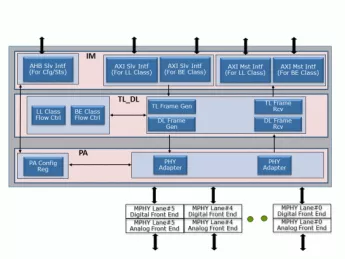

MIPI LLI Controller - (Low Latency Interface)

- Compliant with MIPI LLI Rev 1.0 and M-PHY Type 1 Rev 2.0

- Interfaces to on-chip interconnect infrastructure, like AHB or AXI or OCP buses

- Configurable to provide any or all of the following interfaces for the named traffic classes

- Provides AHB/AXI/OCP Slave Interface for PHY Adapter Layer management

-

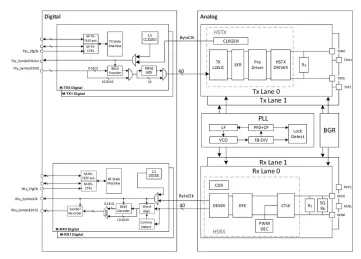

MIPI M-PHY HS-G4 IP (M-PHY v4.1) in TSMC 40G

- Supports MIPI® Alliance Specification for M- PHY® Version 4.1.

- Dual-simplex point-to-point interface with ultra-low voltage differential signaling.

- Slew-rate control for EMI reduction.

-

MIPI M-PHY

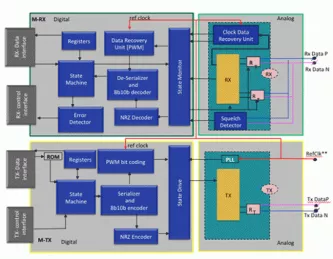

- Innosilicon M-PHY implements MIPI M-PHY protocol V4.1

- The M-PHY protocol specification is a part of a group of communication protocols defined by MIPI® Alliance standards intended for mobile system chip to chip communications

- The M-PHY specification is specifically designed to be suitable for multiple protocols and for a wide range of applications

-

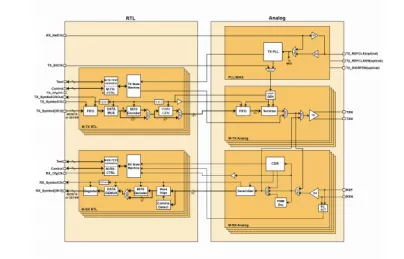

MIPI M-PHY G4 Designed For TSMC 28nm HPC+

- Compliant to MIPI Alliance Standard for M-PHY specification Version 4.1

- Supports M-PHY Type-I system

- Support for Clock and Data Recovery Options

-

MIPI M-PHY - UMC 40nm

- Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

-

MIPI M-PHY in SMIC 90LL

- Supports MIPI Standard for M-PHY v3.0.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

-

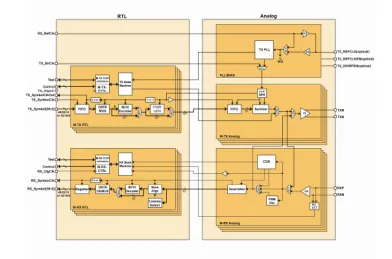

MIPI M-PHY Designed For TSMC 28nm

- •Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

MIPI M-PHY in SMIC 130nm

- Complies with MIPI Standard for M-PHY v3.0

- Slew-rate control for EMI reduction

- Supports HS modes GEAR 1-3

-

MIPI M-PHY (HS-G3) in GF 28LP

- Complies with MIPI Standard for M-PHY v3.0

- Dual-simplex point-to-point interface with ultra low voltage differential signaling