MIPI A-PHY IP

As part of the MIPI (Mobile Industry Processor Interface) standard, MIPI A-PHY IP enables reliable data transmission between sensors, cameras, displays, and other automotive components, ensuring seamless connectivity in modern vehicles. With its ability to deliver high bandwidth over long distances, MIPI A-PHY IP is crucial for advanced driver-assistance systems (ADAS), autonomous driving, and in-vehicle infotainment systems. Offering low latency and robust signal integrity, MIPI A-PHY IP is the ideal solution for powering the next generation of automotive technologies.

All offers in

MIPI A-PHY IP

Filter

Compare

6

MIPI A-PHY IP

from 5 vendors

(1

-

6)

-

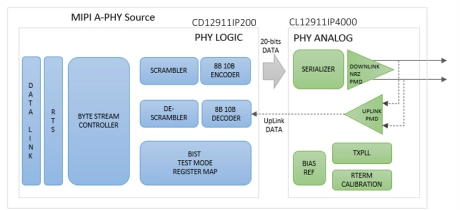

Sensor / Display MIPI A-PHY Source IP

- The CL12911IP4000 is based on MIPI A-PHY interface specification announced in year 2020, targeting ultra-high-speed networking applications in ADAS and autonomous drive subsystems.

- It supports applications that require long reach (up to 15 meters), error-free links, and high EMI immunity requirement.

-

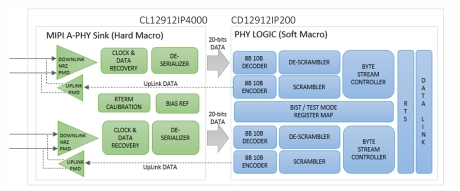

Sensor/Display MIPI A-PHY Sink IP

- The CL12912IP4000 is based on MIPI A-PHY interface specification announced in year 2020, targeting ultra-high-speed networking applications in ADAS and autonomous drive subsystems.

- It supports applications that require long reach (up to 15 meters), error-free links, and high EMI immunity requirement.

-

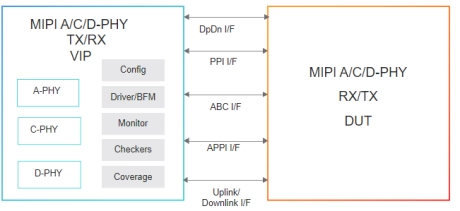

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

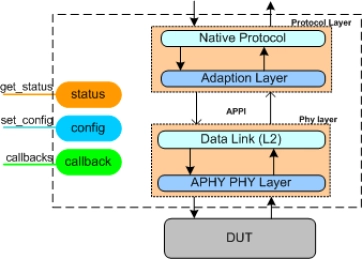

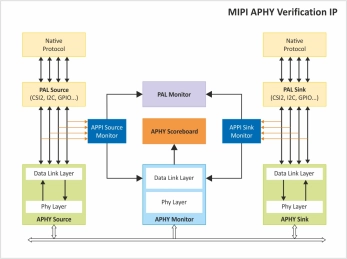

MIPI A-PHY Verification IP

- Implemented in native OpenVera, SystemVerilog, Verilog and SystemC.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Supports MIPI A-PHY specification version upto 2.0.

- Supports single lane and dual lane, point-to-point and serial communication technology.

-

A-PHY v1.1 Verification IP

- Compliant to MIPI A-PHY Specification Version 1.1.1 with APPI interface.

- Support all C-Port, D-Port and Q-Port.

- Support for both Profile 1 and Profile 2.

- Supports all possible configuration for Data Lane Module at PHY layer.

-

MIPI A-PHY

- Asymmetric data link layer with point-to-point or daisy-chain topology

- Up to 15-meter reach

- Support 3 downlink speed gears Gear 1.0/2.0/3.0(2, 4, 8Gbps)

- 2 uplink speed gears (100 and 200 Mbps)

- Ultra-low packet error rate (PER) of 10-19 for unprecedented reliability over vehicle lifetime