CCIX IP Cores

The CCIX (Cache Coherent Interconnect for Accelerators) standard was created to enable hardware accelerators and processors to maintain cache coherency across shared memory in a heterogeneous multi-processor system. It leverages PCI Express 4.0 line rates up to 16GT/s with extended speed mode to accelerate speeds up to 25GT/s for CCIX 1.0 as well as 32GT/s for CCIX 1.1.

Explore our vast directory of CCIX IP Cores below.

All offers in

CCIX IP Cores

Filter

Compare

4

CCIX IP Cores

from 3 vendors

(1

-

4)

-

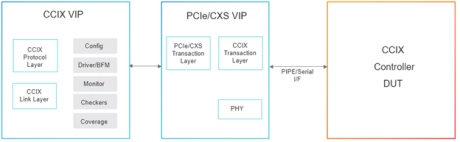

Simulation VIP for CCIX

- CCIX Protocol Layer

- Fully models the CCIX Protocol Layer

- CCIX Transport Layer

- Should be used in conjunction with either CXS or PCIe VIP which model the Transport Layer

-

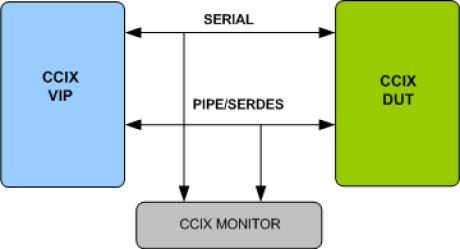

CCIX 1.0 Verification IP

- Supports CCIX Base Specification revision 1.0 version 1.0

- Support all Write, Read, Data less and Atomic transaction.

- Supports all Request responses and Snoop responses.

- Device and Normal memory types support.

-

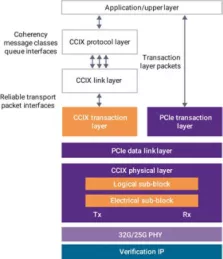

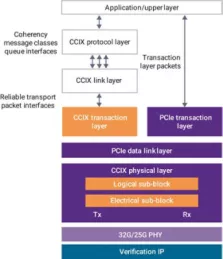

CCIX 32G Premium Controller with AMBA bridge II

- Supports all required features of the CCIX 1.1 specification, including 32GT/s, and ESM support for 25GT/s and 20GT/s

- Supports all required features of the PCIe 4.0 (16 GT/s), 3.1 (8 GT/s), 2.1 (5 GT/s), 1.1 (2.5 GT/s) and PIPE (8-, 16- and 32-bit) specifications

- Choice of datapath widths (128-bit, 256-bit, or 512-bit)

- Supports cache-coherency as defined by the CCIX standard

-

CCIX 32G Premium Controller II

- Supports all required features of the CCIX 1.1 specification, including 32GT/s, and ESM support for 25GT/s and 20GT/s

- Supports all required features of the PCIe 4.0 (16 GT/s), 3.1 (8 GT/s), 2.1 (5 GT/s), 1.1 (2.5 GT/s) and PIPE (8-, 16- and 32-bit) specifications

- Choice of datapath widths (128-bit, 256-bit, or 512-bit)

- Supports cache-coherency as defined by the CCIX standard