Hash and HMAC Accelerator IP for TSMC

Welcome to the ultimate Hash and HMAC Accelerator IP for TSMC hub! Explore our vast directory of Hash and HMAC Accelerator IP for TSMC

All offers in

Hash and HMAC Accelerator IP

for TSMC

Filter

Compare

4

Hash and HMAC Accelerator IP

for TSMC

from 2 vendors

(1

-

4)

-

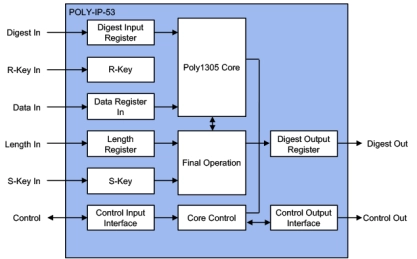

Poly1305 Crypto Accelerator

- Wide bus interface (128-bit data, 128-bit keys, 135-bit digest) or 32-bit register interface

- Key size: 128 bits

- Includes initialization stage

- Supports continuation mode

- Fully synchronous design

-

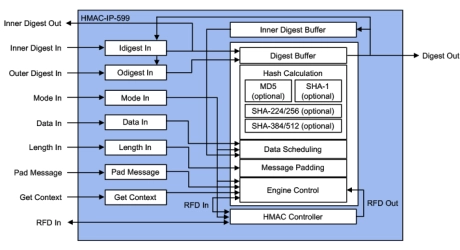

SHA-1, SHA-2, SHA-3 Hash based HMAC, accelerators

- HMAC-IP-59 (EIP-59) is IP for accelerating the various single pass HMAC (FIPS-198-1) algorithms using secure hash integrity algorithms like MD5 (RFC1231), SHA-1 (FIPS-180-2), SHA-2 (FIPS-180-3/4) and SHA-3 (FIPS-202), up to 8 Gbps.

- Designed for fast integration, low gate count and full transforms, the HMAC-IP-59 accelerators provide a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

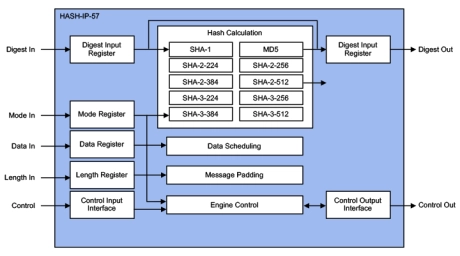

SHA-3, SHA-2, SHA-1, SM3, MD5, Hash Accelerators

- The HASH-IP-57 (EIP-57) is IP for accelerating the various secure hash integrity algorithms like MD5 (RFC1231), SHA-1 (FIPS-180-2), SHA-2 (FIPS-180-3/4) and SHA-3 (FIPS-202), supporting the NIST MAC mode up to 6.4 Gbps @ 450MHz.

- Designed for fast integration, low gate count and full transforms, the HASH-IP-57 accelerators provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

TSMC CL015G 150nm Clock Generator PLL - 130MHz-650MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.