USB 3.0 IP for TSMC

Welcome to the ultimate USB 3.0 IP for TSMC hub! Explore our vast directory of USB 3.0 IP for TSMC

All offers in

USB 3.0 IP

for TSMC

Filter

Compare

21

USB 3.0 IP

for TSMC

from 7 vendors

(1

-

10)

-

USB3.0 build-in clock PHY, TSMC 55LP

- Smallest USB 3.2 Gen1x1 BCK PHY IP worldwide (e.g. IP size @40nm <0.36mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1, 2.0, and 1.1 electrical specifications

- Supports clock outputs from the internal BCK module

- Real-time calibrations to ensure frequency accuracy

-

USB3.0 build-in clock PHY, TSMC 55LP, type-C

- Smallest USB 3.2 Gen1x1 BCK PHY IP worldwide (e.g. IP size @40nm <0.36mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1, 2.0, and 1.1 electrical specifications

- Supports clock outputs from the internal BCK module

- Real-time calibrations to ensure frequency accuracy

-

USB3.0 build-in clock PHY, TSMC 22ULP 1.8V, N/S orientation, type-C

- Smallest USB 3.2 Gen1x1 BCK PHY IP worldwide (e.g. IP size @40nm <0.36mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1, 2.0, and 1.1 electrical specifications

- Supports clock outputs from the internal BCK module

- Real-time calibrations to ensure frequency accuracy

-

USB3.0 build-in clock PHY, TSMC 22ULL 2.5V, N/S orientation, type-C

- Smallest USB 3.2 Gen1x1 BCK PHY IP worldwide (e.g. IP size @40nm <0.36mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1, 2.0, and 1.1 electrical specifications

- Supports clock outputs from the internal BCK module

- Real-time calibrations to ensure frequency accuracy

-

USB3.0 build-in clock PHY, TSMC 22ULL 1.8V, N/S orientation, type-C

- Smallest USB 3.2 Gen1x1 BCK PHY IP worldwide (e.g. IP size @40nm <0.36mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1, 2.0, and 1.1 electrical specifications

- Supports clock outputs from the internal BCK module

- Real-time calibrations to ensure frequency accuracy

-

USB 3.0 PHY

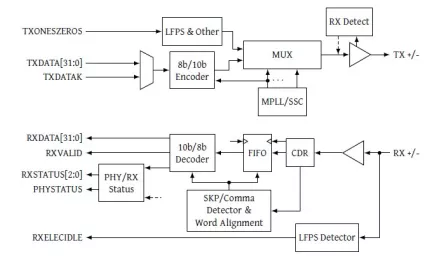

- Standard PHY interface (PIPE) enables multiple IP sources for USB 3.0 Link Layer

- Supports 5.0 GT=s serial data transmission rate

- Supports 16- or 32-bit parallel interface

- Supports PCLK as PHY output

-

PCIe 3.0/3.1/USB3.0/SATA3 Combo PHY

- Standard PHY interface enables multiple IP sources for PCI Express Logical Layer and provides a target interface for PCI Express PHY vendors.

- Supports 2.5Gb/s only or 2.5Gb/s,5.0Gb/s and 8.0Gb/s serial data transmission rate

- Utilizes 8-bit, 16-bit or 32- bit parallel interface to transmit and receive PCI Express data

- Allows integration of high speed components into a single functional block as seen by the endpoint device designer.

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 16FFC

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled

-

USB 3.0 PHY in TSMC (65nm, 55nm, 40nm, 28nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)