Broadcast IP for TSMC

Welcome to the ultimate Broadcast IP for TSMC hub! Explore our vast directory of Broadcast IP for TSMC

All offers in

Broadcast IP

for TSMC

Filter

Compare

19

Broadcast IP

for TSMC

from 11 vendors

(1

-

10)

-

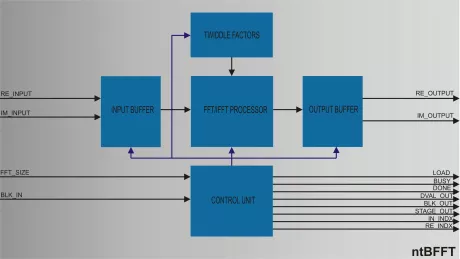

Fully Configurable Radix 2 FFT/IFFT Processor

- Radix-2 Fast Fourier Transform processor IP Core.

- Same IP core may be used to compute both FFT and IFFT transforms without any complexity overhead.

- Highly parameterizable/scalable design using generic I/O fixed point precision and generic internal calculations precision.

- Bit true Matlab script model is provided to aid core fixed point precision configuration for any target application.

-

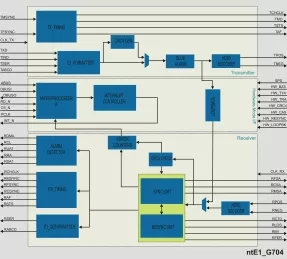

ITU G.704 E1 Framer/Deframer

- E1 framer/deframer compliant to G.704, G.706, G.732 and O.163 ITU recommendations.

- Supports CAS and CCS signalling standards.

- Supports CRC4 based framing standards.

- User configurable receive and transmit control.

-

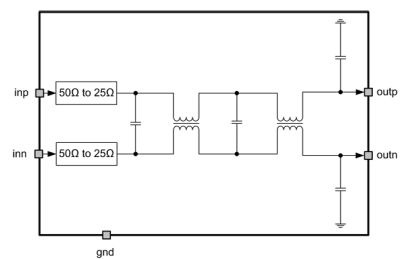

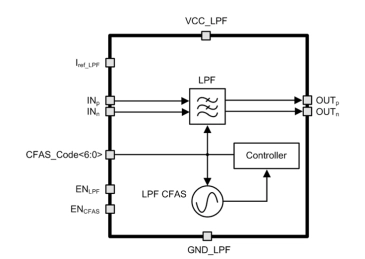

150 MHz 5th order passive LPF

- TSMC 65 nm CRN65LP

- Differential inputs, outputs

- Fixed cut-off frequency 150 MHz

- High linearity

-

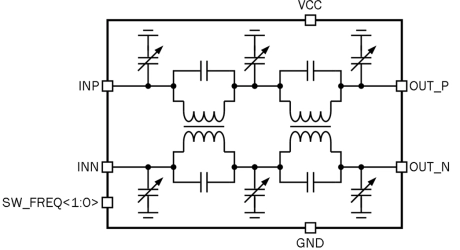

25/50/100 MHz 5th order passive LPF

- TSMC 65 nm CRN65LP

- Differential inputs, outputs

- Fixed cut-off frequency: 25 MHz, 50 MHz, 100 MHz

- High linearity

-

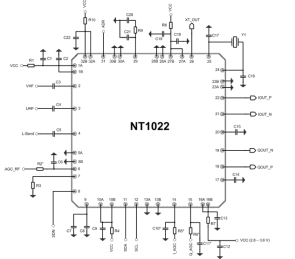

VHF/ UHF/L (DVB-H, DMB and ISDB-T) RF Front-end

- TSMC BiCMOS SiGe 180 nm technology

- Direct conversion receiver

- A few number of external components

- 0.18 um SiGe BiCMOS technology

-

6.5 to 23 MHz 3rd order low pass filter

- TSMC BiCMOS SiGe 180 nm

- Wide cut-off frequency adjustment range (6.5 MHz…23 MHz)

- Low pass filter cut-off frequency adjustment system

- Portable to other technologies (upon request)

-

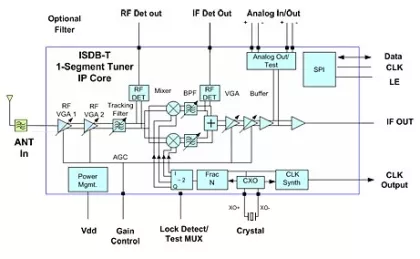

ISDB-T1, Segment Tuner (470-860MHz UHF)

- High Performance

- Configurable 3/4 wire controller

- Self calibrating and programmable filter corner frequencies

- 8 Bit electronically tunable tracking filter

-

12-bit 250MHz interpolation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

12-bit 250MHz Decimation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

Fast Fourier Transformation

- The FFT is a fully customizable FFT. The key features are free choose of the FFT dimension, data width and an additional output with the absolute value of the spectrum.