Serdes IP for Samsung

Welcome to the ultimate Serdes IP for Samsung hub! Explore our vast directory of Serdes IP for Samsung

All offers in

Serdes IP

for Samsung

Filter

Compare

14

Serdes IP

for Samsung

from 4 vendors

(1

-

10)

-

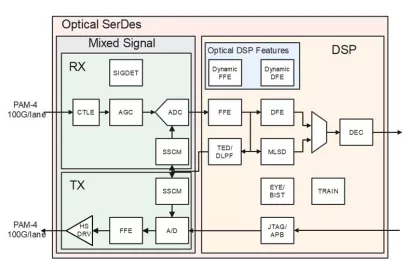

1-112Gbps Integrated Laser Driver and Optical SerDes

- Optical Optimization:

- Integrated laser driver

- RX front-end architected for optical signaling

- Non-linear DSP equalization that corrects for both static and dynamic nonlinearity components.

-

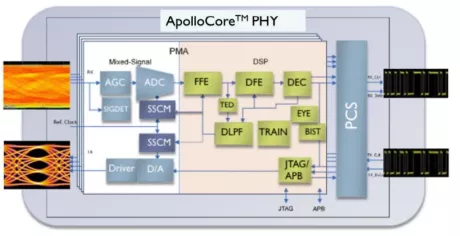

1-112Gbps Medium Reach (MR) and Very Short Reach (VSR) SerDes

- High speed performance

- Low power architecture

- Sub-sampling clock multiplier

-

PCI Express Gen5 SERDES PHY on Samsung 8LPP

- Industry leading low power PMA macro – 224mW per lane at 28Gbps (8.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.38 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen4 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 132.7mW per lane at 16Gbps (8.4mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.32 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen3/4 Enterprise Class SERDES PHY on Samsung 14LPP

- Industry leading low power PMA macro – 132.7mW per lane at 16Gbps (8.4mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.266 mm2 active silicon area per lane including ESD

- Enterprise class Long Reach 5-tap DFE supporting beyond standard PCIe Channels

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 36mW per lane at 8Gbps (4.5mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.1 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

XAUI PHY

- Idle is substituted as K,R or A in Transmit Direction

- K,R and A are substituted back to Idle in Receive Direction

-

8G Multi-SerDes For PCIe3.0/USB3.0 PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive:

-

5G Multi-SerDes For PCIe2.0/USB3.0 PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive:

-

32G Multi-SerDes For PCIe5.0/USB3.x PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive: