PCI IP for Samsung

Welcome to the ultimate PCI IP for Samsung hub! Explore our vast directory of PCI IP for Samsung

All offers in

PCI IP

for Samsung

Filter

Compare

45

PCI IP

for Samsung

from 4 vendors

(1

-

10)

-

PHY for PCIe 6.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

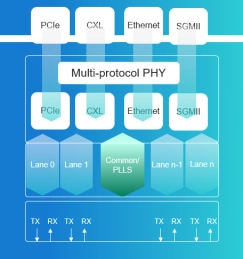

PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0

- Wide range of protocols that support networking, high-performance computing (HPC), and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- User-friendly graphical interface provides easy access to embedded bit-error-rate (BER) and pattern testers and monitors to measure the link performance in real time

-

PCIe 4.0 PHY, SS14LPP x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, SS14LPP x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

20G PHY for PCIe 4 PHY, SS SF4X x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

20G PHY for PCIe 4 PHY, SS SF4E x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, SS 8LPU x4, North/South (vertical) poly orientation for Automotive, ASIL B Random, AEC-Q100 Grade 1

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, SS 14LPU x4, North/South (vertical) poly orientation for Automotive AEC-Q100 Grade 1

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, SS 14LPU x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, SS 14LPP x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver