USB 3.0 IP for GLOBALFOUNDRIES

Welcome to the ultimate USB 3.0 IP for GLOBALFOUNDRIES hub! Explore our vast directory of USB 3.0 IP for GLOBALFOUNDRIES

All offers in

USB 3.0 IP

for GLOBALFOUNDRIES

Filter

Compare

10

USB 3.0 IP

for GLOBALFOUNDRIES

from 6 vendors

(1

-

10)

-

USB3.0 PHY

- Silicon proven in 22, 28, Global Foundries and Samsung

- Spread Spectrum clock (SSC) and data scrambling to minimize EMI

- Supports 16-bit 250-MHz , and 32-bit 125M PIPE interface

- Multiple loopback and compliance test modes

-

USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI

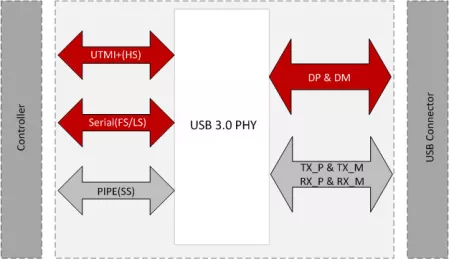

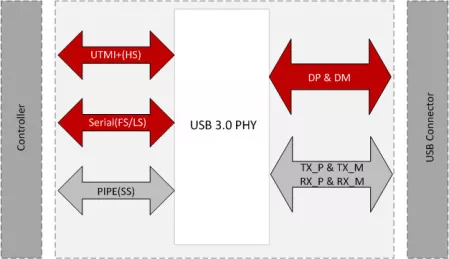

- The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification.

- It supports the USB3.0 5Gbps Super-Speed mode and backward compatibles with the USB2.0 480Mbps High-Speed, 12Mbps Full-Speed, and 1.5Mbps Low-Speed modes

- The USB 3.0 PHY interface complies with PHY Interface for PCI Express and USB3.0 Architectures specification (PIPE 3.0) and the USB2.0 PHY interface complies with the UTMI v1.05 specification.

-

GLOBALFOUNDRIES 22nm FDSOI USB3.0 PHY

- 5-Gbps Super-Speed data transmission rate through 3-m USB3.0 cable

- Spread Spectrum clock (SSC) and data scrambling to minimize EMI

- PIPE 3-compliant Super-Speed USB 3.0 Transceiver interface

- Supports 16-bit 250-MHz , and 32-bit 125M PIPE interface

-

USB 3.0 SSPHY in GF (22nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)

-

PCIe 3.0/3.1/USB3.0/SATA3 Combo PHY

- Standard PHY interface enables multiple IP sources for PCI Express Logical Layer and provides a target interface for PCI Express PHY vendors.

- Supports 2.5Gb/s only or 2.5Gb/s,5.0Gb/s and 8.0Gb/s serial data transmission rate

- Utilizes 8-bit, 16-bit or 32- bit parallel interface to transmit and receive PCI Express data

- Allows integration of high speed components into a single functional block as seen by the endpoint device designer.

-

USB 3.0 PHY in GF (65nm, 55nm, 40nm, 28nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)

-

USB 3.0 femtoPHY in GF (28nm, 12nm)

- Complete mixed-signal physical layer for USB 3.0 applications

- Includes all circuitry needed for operation at all USB speeds (SuperSpeed, High-Speed, FullSpeed, Low-Speed)

- USB-C 3.0 femtoPHY supports Type-C reversible connectors

- Optimized PHY area (<0.5mm2 for USB 3.0, <0.8mm2 for USB-C 3.0)

-

USB 1.1 Transceiver

- USB transceiver is fully support to Standard USB Rev.1.1

- Low power consumption.

- Handle full speed (12Mbs), low speed (1.5Mbs) and suspension mode.

-

USB1.1 Transceiver

- Complies with Universal Serials Bus Specification 1.1

- Utilizes digital inputs and outputs to transmit and receive USB cable data

- Support 12Mbit/s “Full Speed” and 1.5Mbit/s “Low Speed” serial data transmission

- Supports single-ended data interface

-

USB 3.0 PHY

- 5-Gbps SuperSpeed data transmission rate through 3-m USB 3.0 cable

- Spread Spectrum clock (SSC) generation and absorption