The Glasswing family is a set of configurable PHY IPs designed and optimized for in-package applications that do not require a silicon interposer.

GW12-500-USR provides 500 Gbit/s of full-duplex system bandwidth at a power consumption as low as 1 pJ/bit, through the use of CNRZ-5 Chord™ Signaling and a forwarded clock architecture. Glasswing IP may be deployed in multiple instances to provide efficient extended interfaces

Ultra-short reach SerDes with 500 Gbit/s throughput

Overview

Key Features

- MCM interface consisting of four 6-wire CNRZ-5 Chords, plus a shared forwarded clock (26 wires total per direction)

- No silicon interposer required due to standard 150 um bump pitch

- Maximum throughput of 500 Gbit/s in each direction

- Line rate programmable from 12.5 to 25 GBd for a throughput of 62.5 to 125 Gbit/s per Chord

- Total throughput configurable by selecting number of active Chords

- TX and RX data buses consisting of five 32-bit data words (plus clock) for each Chord

- Simple word-based TX to RX interface, RX logic recovers data alignment

- DC-coupled link with no coding/framing requirements; light-weight scrambler in PMA Soft IP ensures sufficient data toggling

- Configuration and link start-up through APB (ARM Peripheral Bus) interface

- Internal TX to RX loopback for wafer/die level test

- Configurable Bolt-On PMA soft IP for ease of use:

- Scrambler

- Bit error iniection

- Single cycle FEC to decrease BER/increase link length

- Including option to include PRBS to test impact on BER using FEC

- Far-end loopback

- RX CTLE equalization for up to 6 dB channel loss at 12.5 GHz

- TX PLL with reference clock input frequency from 100 MHz to 312.5 MHz (25 MHz supported for Test)

- Supports JTAG boundary scan (1149.1) and scan test modes (Shift/Capture and Bypass)

- Integrated diagnostics: PRBS-15 and PRBS-31 pattern generation and verification, RX EyeScope

- DFT: at-speed BIST of analog plus stuck-at scan (Capture and At-Speed)

- ATPG support

- JEDEC JESD247 Multi-wire Multi-level Interface Specification compatible

Benefits

- 2x to 4x throughput at 50% or less energy consumption as compared to conventional SerDes over the same number of pins/wires

- High pin-efficiency and low power

- 208.3 Gbit/s full-duplex bandwidth per mm of die edge (500 Gbit/s for 2.4 mm of die edge)

- Supports up to 6 dB channel insertion loss at 12.5 GHz

- NRZ-like ISI and noise performance

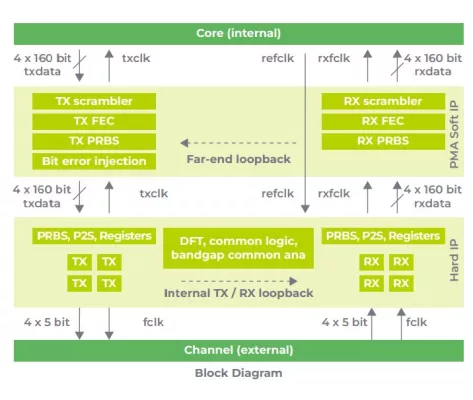

Block Diagram

Applications

- Hyperscalers and data centers

- Aerospace and defense

- Automotive

- 5G infrastructure and equipment

- Consumer space

- AI, ML, deep learning

Deliverables

- Datasheet and application notes

- Hard IP standard integration views: LEF, LIB, SDC, GDSII, LVS netlist, ATPG netlist

- PMA Soft IP

- Verilog Hard IP customer model for system simulation: reference test bench

- Qualification report

- Package design and integration guidelines

Technical Specifications

Foundry, Node

GlobalFoundries® 12LP process

Related IPs

- Scalable Ultra-High Throughput 8/10/12-bit JPEG Encoder with Video Rate Control

- 1-112Gbps Medium Reach (MR) and Very Short Reach (VSR) SerDes

- 112G-VSR PAM4 SerDes PHY - PPA optimized for short reach connectivity

- 32G Multi Rate Long Reach SerDes PHY - GlobalFoundries 12LP and 12LPP

- 32G Multi Rate Very Short Reach SerDes PHY - GlobalFoundries 12LP and 12LPP

- UART with Synchronous CPU Interface