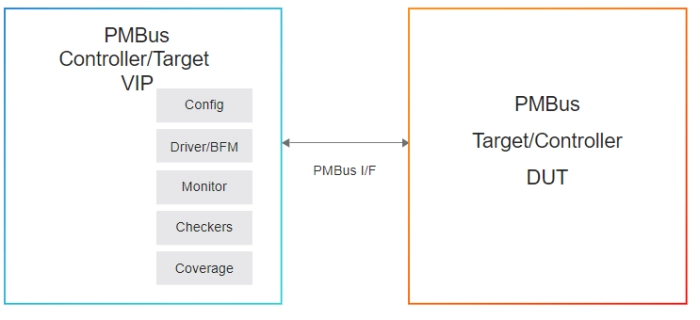

Incorporating the latest protocol updates, the Cadence® Verification IP (VIP) for PMBus provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. The VIP for PMBus is designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, and helps to reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for PMBus runs on all major simulators and supports SystemVerilog verification language along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specification: PMBus v1.3.1 - Power System Management Protocol Specification Part I – General Requirements, Transport And Electrical Interface and Power System Management Protocol Specification Part II – Command Language.