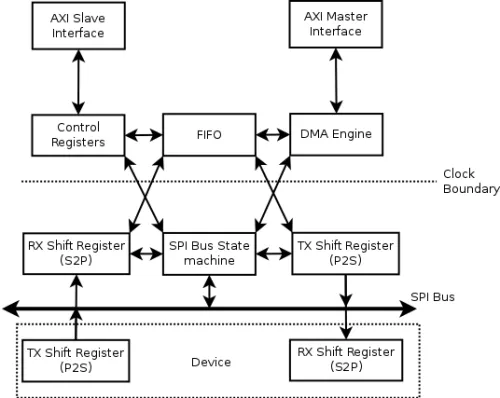

Serial Peripheral Interface (SPI) is a high-speed synchronous serial input/output port IP that allows a serial bit stream of programmed length (2 to 16 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI is normally used for communication between the device and external peripherals. SPI module connects to the DMA Engine. It has an AXI bus interface on the other side for the configuration and control registers of the

Host Controller. The SPI Flash controller is provided to allow direct PIO access to SPI flash devices for BIOS boot up.

Serial Peripherial Interface

Overview

Key Features

- Provides AXI interface

- Provides Interface to DMA

- Provides direct PIO access to SPI flash devices for BIOS boot up

Block Diagram

Applications

- Silicon On Chip design for:

- - Ultra mobile Computers

- - Tablet Computers

- - Smart Phones

Deliverables

- Synthesizable Verilog RTL

- Test bench/Test plan

- IP Integration guidelines/Documentation

Technical Specifications

Foundry, Node

TSMC 28nm

Maturity

Mature

Availability

Now

Related IPs

- Serial RapidIO - Physical Layer Interface

- MIPI CSI-2 host/device controllers for high-speed serial interface between image processor and camera sensors

- Automotive-grade MIPI CSI-2 host/device controllers for high-speed serial interface between image processor and camera sensors

- MIPI DSI-2 controllers with VESA DSC for high-speed serial interface between application processor and displays

- I2S/TDM Serial Audio Interface with Asynchronous Sample Rate Conversion

- Synchronous Serial Interface Controller