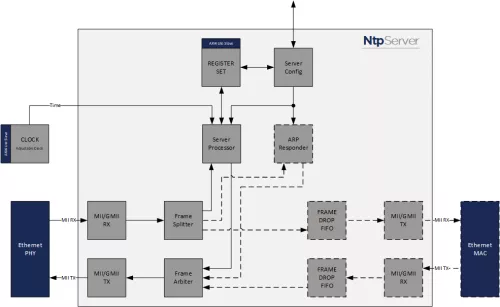

NetTimeLogic’s NTP Server is a full hardware (FPGA) only implementation of a SNTPv4 Server according to RFC 4330/5905. It supports hardware timestamping and insertion with 4ns resolution and repondes to NTP requests from NTP clients fully in hardware which gives an unprecedented performance of 100k+ requests/s (~500k) with minimal resource usage. It supports the NTP unicast, multicast and broadcast mode and can forward non-NTP frames for sharing the same Ethernet port with e.g. a CPU. Conversion from TAI to UTC (taking leap seconds and smearing into account) is completely done in HW. This allows running NTP synchronization completely independent and standalone from the user application. The core can be configured either by signals or by an AXI4Light-Slave Register interface.

Combine it with our NMEA Slave and PPS Slave and build your GPS synchronized Stratum 1 NTP Server

All calculations and corrections are implemented completely in HW.

NTP Server core

Overview

Key Features

- SNTP Server according to RFC 4330/5905 (NTPv4)

- Intercepts path between MAC and PHY

- Single Port

- Ipv4 (IPv6 comming soon)

- Support for Unicast, Multicast or Broadcast NTP mode

- Full line speed, handling 100k+ (~500k) requests

- Hardware timestamping on (R)(G)MII level

- Support for UTC leap second handling (jump or smearing),

- Optional leap second smearing (configurable rate)

- AXI4 Light register set or static configuration

- MII/GMII/RGMII Interface support (optional AXI4 stream for interconnection to 3rd party cores)

- Timestamp resolution with 50 MHz system clock: 10ns, with high resolution clock 4ns

- Hardware PI Servo

Block Diagram