From consumer to industrial, from automotive to healthcare – new algorithms blend digital signal processing and digital signal control for fusing multiple sensors, for interpreting data at the edge, and for connecting to the cloud using multimode wireless connectivity.

As designers are required to efficiently build ever-more complex applications that balance signal processing and control workloads, a new breed of DSP architecture that combines the inherent low power requirements of DSP kernels with high-level programming and compact code size requirements of a large control code base, is required.

The Ceva-BX architecture delivers excellent all-round performance for a new generation of smart devices by providing the perfect alternative for special purpose DSPs and MCUs with DSP co-processors that cannot handle the diverse algorithm needs of today’s applications.

Multipurpose Hybrid DSP and Controller Architecture Family

Overview

Key Features

- Parallel processing SIMD Instruction Set Architecture

- 5-way VLIW micro-architecture

- Single or dual scalar compute engines

- 11-stage pipeline

- Speed of 2 GHz at TSMC 7nm process

- Up to 4.5 CoreMark/MHz score

- Support for neural network edge inference

- Half, single and double precision IEEE floating point units

- Trusted execution modes for high security provisioning

- Fully cached memory subsystem

- Automatic Queue and Buffer management mechanisms to integrate co-processors and create a cluster of Ceva-BX cores

- - Comprehensive software development tool chain, including an advanced LLVM compiler, Eclipse based debugger, DSP and neural network compute libraries, common neural network frameworks support, and choice of industry leading Real Time Operating Systems (RTOS).

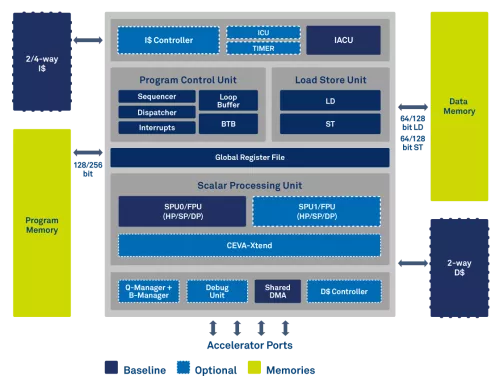

Block Diagram

Applications

- Wireless terminals

- Wireless basestations

- IoT and cellular M2M

- Wireless modems

- Home networking

- RRH

- Audio

- Voice

- Speech Recognition

Technical Specifications

Maturity

In Production

Availability

Available

TSMC

Pre-Silicon:

12nm

Related IPs

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- Multifunctional DSP Architecture for High-Performance, Low-Power Audio/Voice/Sensing and Wireless Communication Applications

- High Performance Scalable Sensor Hub DSP Architecture

- PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- STAR1020 - Ultra low-power hybrid noise cancelling DSP