The MIPI CSI-2 with C-PHY Verification IP provides an effective & efficient way to verify the components interfacing with MIPI CSI-2 with C-PHY interface of an IP or SoC. The MIPI CSI-2 with C-PHY VIP is fully compliant to MIPI Alliance CSI-2 Specification Version 4.0.1 along with MIPI Alliance C-PHY Specification Version 2.1. The VIP is a light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

MIPI CSI-2 with C-PHY Verification IP

Overview

Key Features

- Compliant to MIPI CSI-2 Specification Version 4.0.1 along with MIPI C-PHY Specification Version 2.1 with PPI interface

- Supports upto 32 virtual channels with C-PHY

- C-PHY supports MFEN and SFEN for CSI-2 TX and RX respectively for Data Lane greater than 1

- C-PHY supports MFAA and SFAA for CSI-2 TX and RX respectively for Data Lane 1 module

- Support for a configurable number of lanes.

- Configurable ULPS mode & other CSI-2 configurations using CCI Commands

- Supports CCI (I2C)/CCI (I3C) bidirectional control interface

- Supports all types of Sync Word insertion and detection during data payload transmission

- Supports Data Lane distribution and merging in case of multi-Lane configuration along with filler byte insertion

- Supports Unified Serial Link (USL) to alleviate the use of CCI with a single bidirectional PHY lane (Lane-1)

- Support both LP and ALP modes for USL

- Support for LRTE and data scrambling

- Supports High-Speed, Low Power Escape, Alternate low power (ALP) & Control modes

- Supports 16-bit to 7-symbol Mapper and 7-symbol to 16-bit Demapper

- Supports symbol encoding and decoding

- Supports dynamically configurable modes

- Supports all Short and Long packet formats

- Supports CRC generation and detection

- Supports all primary and secondary CSI-2 data formats

- Supports Frame/ Line Synchronization

- Supports both Data Type Interleaving and Virtual Channel Interleaving frames

- Strong Protocol Monitor with real-time exhaustive programmable checks available for each LLP, LM, PHY layer, and also for PPI.

- Supports Dynamic as well as Static Error Injection scenarios at both Protocol and PHY layer

- On-the-fly protocol checking using assertions

- Built-in Coverage analysis

- Provides a comprehensive user API (callbacks) in Transmitter and Receiver

- Graphical analyzer for all Layers to show transactions for easy debugging

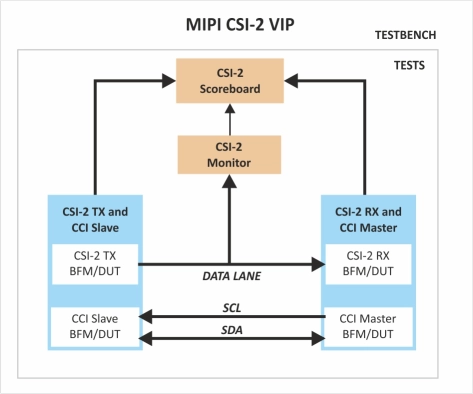

Block Diagram