LVDS Synthesizable Transactor provides a smart way to verify the LVDS component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's LVDS Synthesizable Transactor is fully compliant with standard LVDS Specification and provides the following features.

LVDS Synthesizable Transactor

Overview

Key Features

- Follows LVDS Atmel-42415-WIRELESS-AT86RF215_Datasheet specification

- Supports BBIC and RFIC Mode

- Supports half duplex data transfer

- Supports both data path transaction and SPI control interface transactions

- Supports following IQ data path transaction

- Supports TXD, RXD09 and RXD24

- Supports 2bit I SYNC and Q SYNC data

- Supports 14bit I data and Q data

- Supports error injection

- Supports following SPI control interface transaction

- Supports 2bit command plus 14bit address and 8bit data control field format

- Supports plane power consumption to negligible levels

- Supports Master and Slave Mode

- Supports baud rate selection

- Supports single and burst transfer mode

- Supports various kinds of errors as follows

- I SYNC error

- Q SYNC error

- Invalid zero word error

- Illegal write data error

- Read only address error

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

- Synthesizable transactors

- Complete regression suite containing all the LVDS testcases

- Examples showing how to connect and usage of Synthesiable VIP

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Benefits

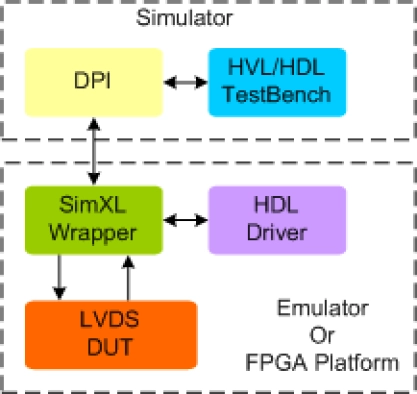

Block Diagram