LDPC Decoder for 5G NR and Wireless

Overview

Mobiveil's 5G NR LDPC Decoder IP Core offers a robust solution for LDPC decoding, featuring a dedicated LDPC decoder block for optimal performance. It employs the Min-Sum LDPC decoding algorithm to ensure efficient decoding. The core allows for programmable internal bit widths at compile time, though the default values are usually sufficient. The core includes an early iteration termination feature based on a concurrent parity check engine, enabling early exit during an iteration. Additionally, the maximum number of iterations can be set during runtime via a wire. The core also supports the accumulation of computed LLRs for failed previous transmissions when using HARQ, enhancing its overall functionality and efficiency in 5G applications.

Key Features

- Provides optimal decoding using the Min-Sum LDPC decoding algorithm

- Internal bit widths are programmable at compile time

- Input LLR bit widths are programmable at compile time, range 5 to 8 bits wide

- Early iterations termination based on concurrent parity check engine

- Early exit in the middle of an iteration based on concurrent parity check engine

- Maximum number of iterations set via wire during run-time

- Accumulation of computed LLRs for failed previous transmissions when using HARQ

- Full support of 5G NR specification (38.212 v17)

- Support for all Base Graphs 1/2 codes

- Additional Measurement Outputs beyond the scope of 5G physical channel measurement specified in 38.215

- Per-block modifiable code block length, code rate, base graph, and maximum number of iterations

- Supports lifting sizes from 2 to 384

- Early termination based on syndrome check on each iteration and layer

- Supports FPGA, ASIC Platforms

Benefits

- Feature rich, highly flexible, scalable, configurable and timing friendly design

- Ease of integration

- Compliance with 3GPP Standards

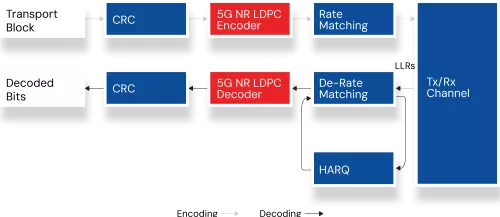

Block Diagram

Deliverables

- Synthesizable parametrized Verilog

- Synthesis scripts

- Test-bench and regression test suite

- Software for generating test vectors

- C++ bit-accurate model

- Documentation

Technical Specifications

Maturity

Silver

Availability

Contact ip@mobiveil.com

Related IPs

- LDPC Encoder / Decoder for 3GPP 5G NR

- Multi-protocol wireless platform integrating Bluetooth Dual Mode, IEEE 802.15.4 (for Thread, Zigbee and Matter)

- 5G-NR LDPC Decoder

- 1Gbit/s LDPC Decoder and Encoder (WiMedia UWB)

- GEO-Mobile Radio (GMR) LDPC Decoder

- IEEE 802.15.3c (60 GHz PHY) Multi-Gbit/s LDPC Decoder