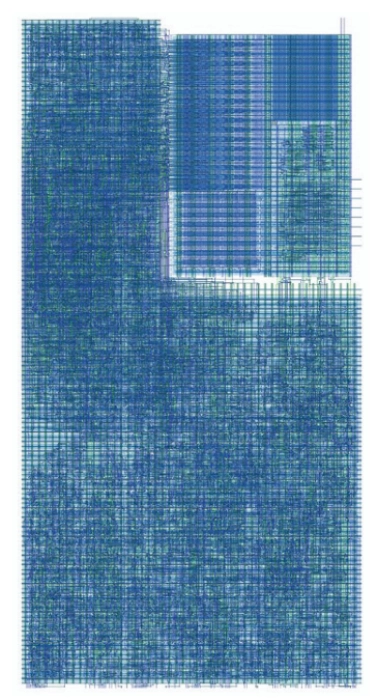

All-digital phase locked loop (ADPLL) clock generator for a nominal frequency of 2 GHz (0.8 V).

The Racyics® all-digital phase locked loop (ADPLL) clock generator is designed to generate a nominal 2 GHz multi-phase clock from a low-frequency reference with as little power and area overhead as possible. For highest flexibility, a wide range of reference frequencies for the Digitally Controlled Oscillator (DCO) is supported.