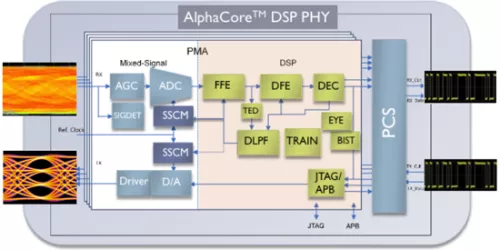

The AlphaCORE Long-Reach (LR) Multi-Standard-Serdes (MSS) IP is a high-performance, low-power, DSP-based PHY. It is a highly configurable IP that supports all leading edge NRZ and PAM data center standards from 1Gbps to 112Gbps, supporting diverse protocols such as PCI-Express Gen1-5 and 1G/10G/25G/50G/100Gbps Ethernet.

The brilliance of the AlphaCORE LR MSS is in its register configurable DSP architecture. The AlphaCORE leverages high-performance A/D converters to digitize incoming data over copper or fiber. The AlphaCORE Master Controller uses complex signal processing techniques to recover the signal, while optimizing both power and latency.

1-112Gbps Long-Reach (LR) Multi-Standard-Serdes (MSS)

Overview

Key Features

- High speed A/D

- The AlphaCORE MSS IP employs a high speed A/D architecture that has configurability for both the A/D sampling rate as well as the A/D resolution

- Sub-sampling clock multiplier

- The AlphaCORE CDR employs a wide tuning, sub-samplingclock multiplier that can track over 5000ppm error for both scrambled and 8B/10B encoded data

- Master controller

- The AlphaCORE DSP Master Controller includes:

- Combination of firmware training with hardware accelerators to provide full flexibility with minimum power state transition times

- Non-destructive, in-service eye monitoring

- IP subsystem

- Alphawave also delivers complete Ethernet and PCIe IP subsystems, including PCS layers and MACs. Our industry leading PHYs and MACs are fully validated and architected for low latency and maximum configurability

- Receive Equalization

- Designed for closed eye, backplane systems up to 36dB of insertion loss at Nyquist for PAM4 and greater than 40dB of loss for NRZ with NEXT. Includes blind adaptive equalizer and channel estimator

- I/O Density

- The AlphaCORE delivers the world’s highest IO density for Long Reach SerDes – greater than 25Tb/s IO capability can be packed on a die less than 250mm²

- Output Driver Swing

- High performance PAM4 and NRZ output DAC delivers maximum long-reach performance with IO swings greater than 1.2V

- Configurability

- Supports 1, 4, 8, 16 lane configurations, different IP options available for north/south versus east/west orientations. The AlphaCORE also supports multiple rows of stacking for high density applications, and can also support multiple different metal options for SOC flexibility.

- Devices Used

- Standard CMOS digital devices

Benefits

Block Diagram