Other

All offers in

Other

Filter

Compare

26

Other

from 15 vendors

(1

-

10)

-

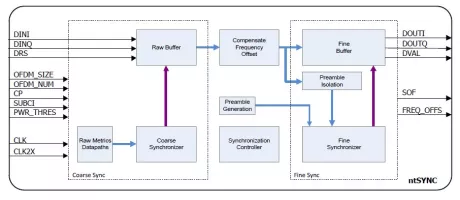

OFDM synchronization unit

- Programmable cyclic prefix, sub-channelization index.

- Based on a proprietary modification of Schmidl-Cox synchronization algorithm.

-

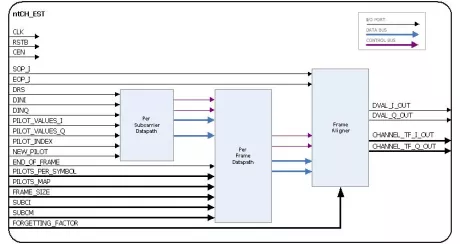

Programmable OFDM Channel Estimator

- Fully configurable, high throughput

- Programmable pilot patterns

-

OFDM Baseband Processor

- Customized transmit and receive physical layer chains.

- Fully synchronous design enabling high throughput TDD operation.

-

-

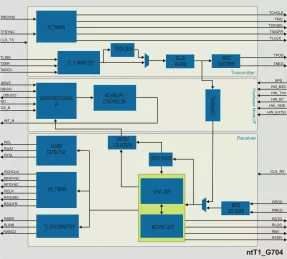

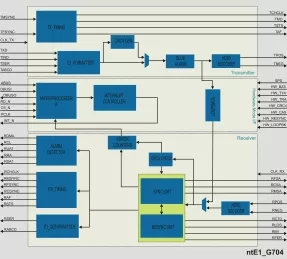

ITU G.704 E1 Framer/Deframer

- E1 framer/deframer compliant to G.704, G.706, G.732 and O.163 ITU recommendations.

- Supports CAS and CCS signalling standards.

- Supports CRC4 based framing standards.

- User configurable receive and transmit control.

-

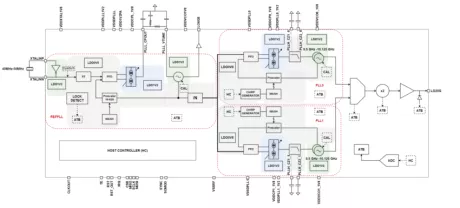

19 GHz to 20.25 GHz FMCW Modulator for RADAR

- Power Dissipation: 480mW

- Output power: 10 dBm

- Reference input: 20 MHz to 100 MHz

-

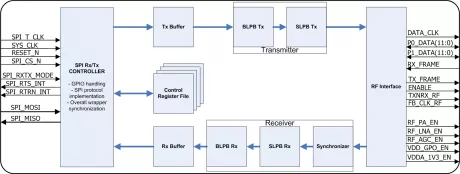

Packet-based Digital Radio Link

- Fully custom solution

- Separate Modulator/Demodulator pair

- FSK or PSK modulation schemes

- Small implementation size

-

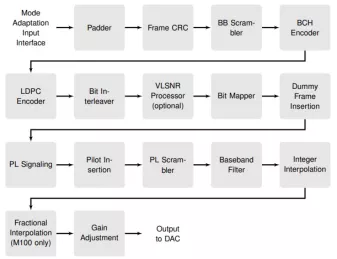

DVB-S2X Modulator

- Compliant with DVB-S2 and DVB-S2X

- Supports ACM, CCM, and VCM modes

- Support for short and normal frames (16,200 bits and 64,800 bits)

- Support for QPSK to 256-APSK

- Support for very low SNR modes (VLSNR) optional

-

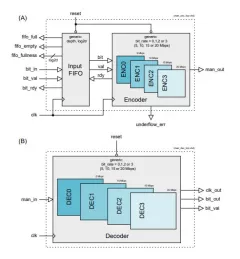

Manchester Encoder / Decoder

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human readable VHDL (or Verilog) source code

-

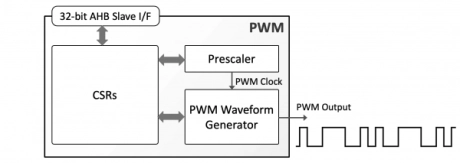

Pulse Width Modulator

- The PWM IP core implements a compact and highly flexible Pulse Width Modulator. The core generates a repeated pattern of pulse trains of run-time configurable period and duty cycle.

- Those pulse trains can be used in a wide variety of applications including but not limited to motor control and LED dimming. They can also be filtered with a lowpass filter to implement Digital to Analog Converters (DAC).