DDR4 Controller IP

Welcome to the ultimate DDR4 Controller IP hub! Explore our vast directory of DDR4 Controller IP

All offers in

DDR4 Controller IP

Filter

Compare

46

DDR4 Controller IP

from 10 vendors

(1

-

10)

-

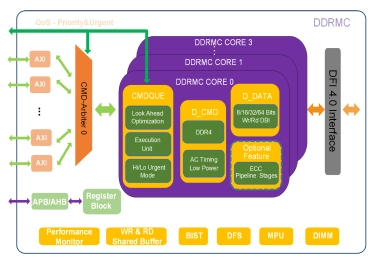

DDR4 Controller

- Maximizes bus efficiency via look-ahead command processing, bank management, auto-precharge and additive latency support

- Latency minimized via parameterized pipelining

- Achieves high clock rates with minimal routing constraints

- Supports half-rate and quarter-rate clock operation

- Supports DDR4 SDRAM 3DS device configurations

-

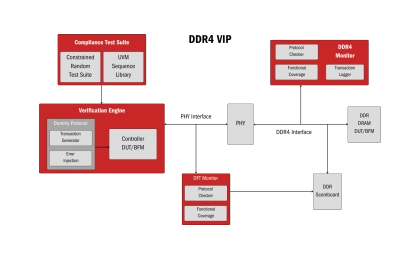

DDR4 Controller - Validates memory compliance, optimizes performance, ensures reliability

- The DDR4 Memory Controller Verification IP ensures compliance with DDR4 standards, validating high-speed data transfer, read/write operations, and error correction. It provides automated testing, advanced debugging tools, and scalability for complex memory systems.

- Designed for versatile applications, this IP optimizes performance in gaming consoles, data centers, AI systems, networking devices, and more. It ensures memory reliability, efficiency, and scalability across industries, accelerating time-to-market for DDR4-based products

-

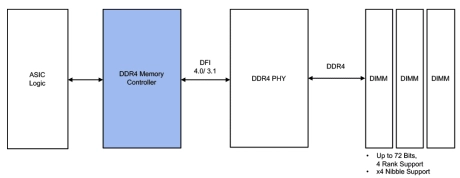

DDR4 IP solution

- Compatible with DDR4 up to 3200Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

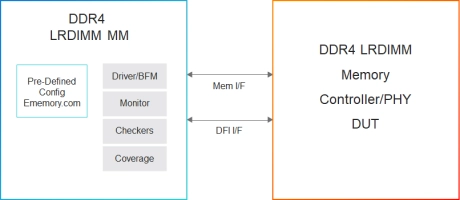

Simulation VIP for DDR4 LRDIMM

- DIMM Types

- DDR4 UDIMM, RDIMM, LRDIMM, DDR4 3DS, 3DS UDIMM, 3DS RDIMM, and 3DS LRDIMM

- LRDIMM Training Modes

- Fully supports DWL, HWL, MREP, MRD, and MWD Training modes

-

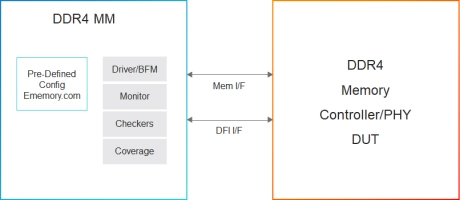

Simulation VIP for DDR4

- Data Width, Density

- 4, 8, and 16. 2 Gb to 16 Gb

- Speed

- 1600, 1866, 2133, 2400, 2666, and 3200

-

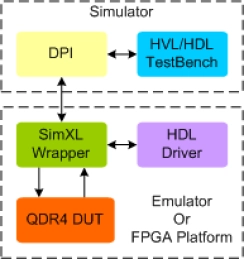

QDR4 Synthesizable Transactor

- Supports 100% of QDR4 protocol standard CY7C4142KV13

- Supports 144-Mbit density (8M × 18, 4M × 36)

- Supports eight-bank architecture enables one access per bank per cycle

- Supports two-word burst on all accesses

-

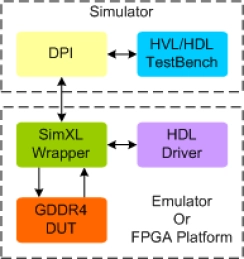

GDDR4 Synthesizable Transactor

- Supports 100% of GDDR4 protocol standard GDDR4Spec rev 04

- Supports all the GDDR4 commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports all mode registers programming

-

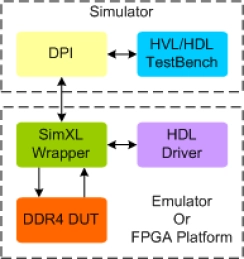

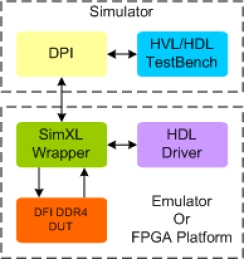

DDR4 DFI Synthesizable Transactor

- Compliant with DFI version 3.0 or higher Specifications.

- DFI-DDR4 Applies to :

- DDR4 protocol standard JESD79-4, JESD79-4A, JESD79-4A_r2,JESD79-4B, JESD79-4C and JESD79-4D (draft) Specification

- Supports all Interface Groups.

-

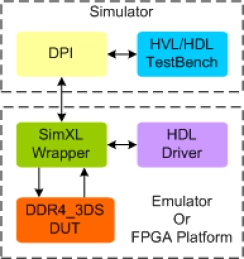

DDR4 3DS Synthesizable Transactor

- Supports 100% of DDR4 3DS protocol standard JESD79-4-1, JESD79-4-1A and JESD79-4-1B

- Supports all the DDR4 3DS commands as per the specs

- Supports up to 16 GB device density

- Supports X4 and X8 devices types

-

DDR4 Synthesizable Transactor

- Supports 100% of DDR4 protocol standard JESD79-4, JESD79-4A, JESD79-4A_r2, JESD79-4B, JESD79-4C and JESD79-4D(Draft)

- Supports all the DDR4 commands as per the specs

- Supports up to 16GB device density

- Supports X4,X8,X16 and X32 devices