MIPI M-PHY IP

The MIPI M-PHY IP is a physical layer interface IP designed for the latest generation of flash memory-based storage and for other high-bandwidth applications that require fast communications channels. The specification, which uses a differential signaling with an embedded clock, is optimized for applications that have a particular need for high data rates, low pin counts, lane scalability and power efficiency. Key applications include connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

All offers in

MIPI M-PHY IP

Filter

Compare

76

MIPI M-PHY IP

from 12 vendors

(1

-

10)

-

MIPI M-PHY G4 Designed For TSMC 28nm HPC+

- Compliant to MIPI Alliance Standard for M-PHY specification Version 4.1

- Supports M-PHY Type-I system

- Support for Clock and Data Recovery Options

-

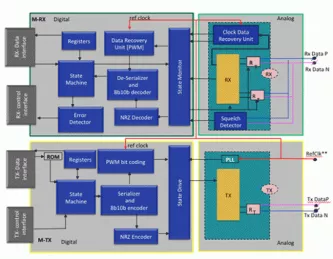

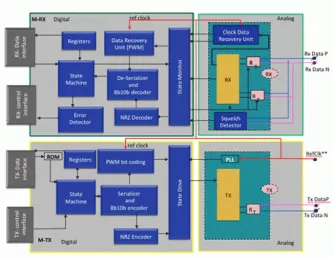

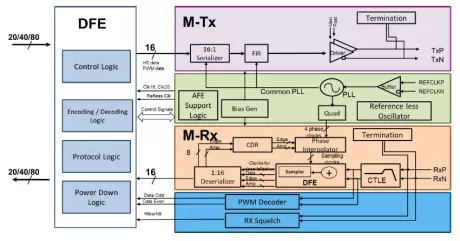

MIPI M-PHY - TSMC 40nm

- Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

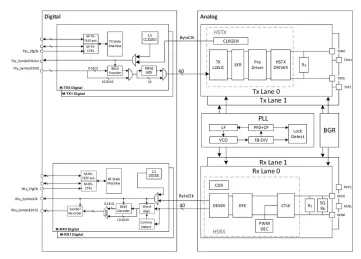

MIPI M-PHY HS-G4 IP (M-PHY v4.1) in TSMC 40G

- Supports MIPI® Alliance Specification for M- PHY® Version 4.1.

- Dual-simplex point-to-point interface with ultra-low voltage differential signaling.

- Slew-rate control for EMI reduction.

-

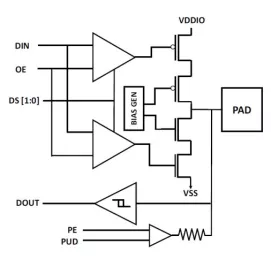

1.8V/3.3V Switchable GPIO With 5V I2C Open - Drain & Analog Cells in Samsung 11nm LPP

- Multi-voltage 1.8V / 3.3V switchable operation

- 4 selectable drive strengths (25-235 MHz @ 1.8V, 10pF

- Full-speed output enable

-

MIPI 4.1 M-PHY HS Gear 4

- Supports high speed data transfer G4A/B and backward compatible

- Multi-lane compatible

- Supports 4 reference clocks as per MIPI 4.1 specification

-

MIPI M-PHY Designed For GF 28nm

- •Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

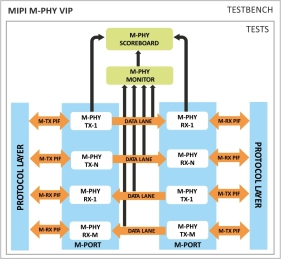

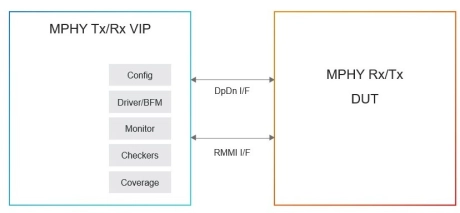

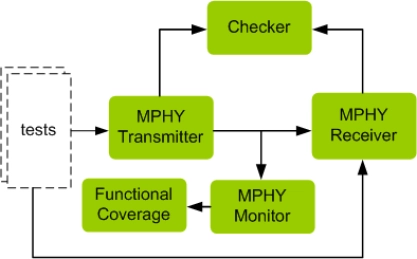

MIPI M-PHY Verification IP

- Compliant to MIPI M-PHY Version 5.0

- Supports two SUB-LINKs with configurable number of LANEs in each

- Supports high speed and low speed modes for all modules

- Supports HS-BURST with all HS-GEARs, HS-G1 to HS-G3 in HS-MODE

-

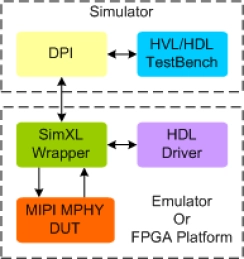

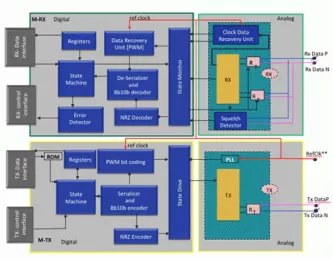

Simulation VIP for MIPI M-PHY

- Specification Compliance

- Complies with MIPI M-PHY 4.0, 4.1 and 5.0 specification

- M-PHY Type 1 and Type 2

- Supports Type 1 and Type 2

-

MIPI MPHY Verification IP

- Supports 3.0,4.1 and 5.0 MIPI MPHY Specification.

- Support Type-1 and Type-II operations.

- Supports both serial and protocol layer interface.

- Supports all PWM 0-7 gear of operation.

-

MIPI MPHY Synthesizable Transactor

- Supports 3.0, 4.0 MIPI MPHY Specification

- Support Type-1 and Type-II operations

- Supports both serial and protocol layer interface

- Supports all PWM 0-7 gear of operation