MIPI PHY IP

MIPI PHY IP IP solutions provide the physical layer communication for various MIPI interfaces, ensuring robust signal integrity and low-power operation. Key offerings include MIPI D-PHY IP, ideal for high-speed video and imaging applications, MIPI C-PHY IP, designed for optimized performance in mobile devices, and MIPI A-PHY IP, which supports automotive applications with long-range, high-speed capabilities. Additionally, the MIPI C-PHY/D-PHY Combo IP offers versatility for devices requiring both high-speed data and video transmission. With the MIPI M-PHY IP, advanced mobile and data storage solutions can achieve peak performance, making MIPI PHY IP a cornerstone for next-generation connectivity.

All offers in

MIPI PHY IP

Filter

Compare

577

MIPI PHY IP

from 29 vendors

(1

-

10)

-

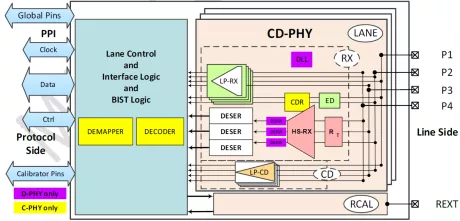

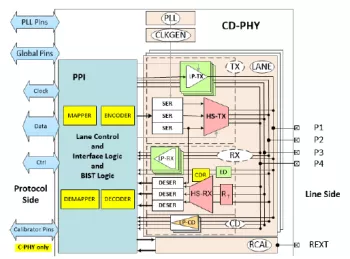

MIPI C-PHY/D-PHY Combo CSI-2 RX+ IP (6.0Gsps/trio, 4.5Gbps/lane) in TSMC N6

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

MIPI C-PHY/D-PHY Combo RX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

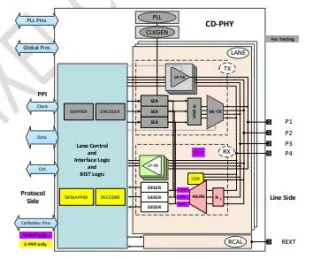

MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI Alliance Standard for C-PHY specification Version 1.2

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

-

MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI for C-PHY specification Version 1.2

- Compliant to MIPI for D-PHY specification Version 1.2

-

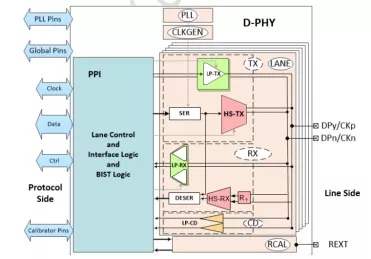

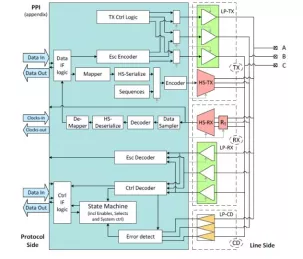

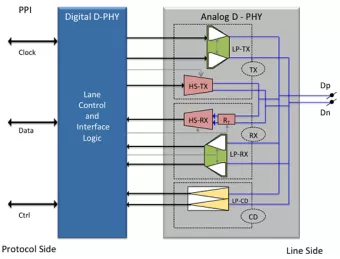

MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI Alliance Standard for D-PHY specification Version 2.1, 1.2, 1.1

- Supports standard PHY transceiver compliant to MIPI Specification

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

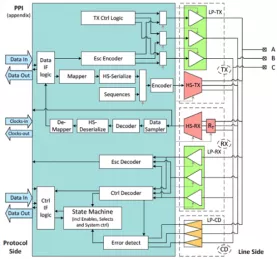

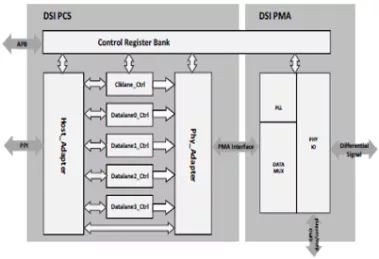

MIPI D-PHY Tx IP, Silicon Proven in TSMC 22ULP

- DSI PCS :

- The Register Bank is accessible through a standard AMBA-APB slave interface, providing access to the DSI PHY registers for configuration and control.

- Host_adapter: remapping PPI Signal with lane control and phy_adapter block;

- Lane_ctrl block (clklane_ctrl/datalane0_ctrl/datalane1_ctrl/datalane2_ctrl/datalane3_ctrl)

-

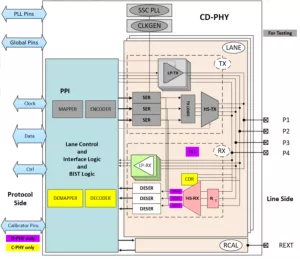

MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

MIPI C-PHY/D-PHY Combo RX IP 4.5Gsps/4.5Gbps in TSMC N7

- Dual mode PHY Supports MIPI Alliance Specification D-PHYv2.5 & C-PHYv2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHYmode

-

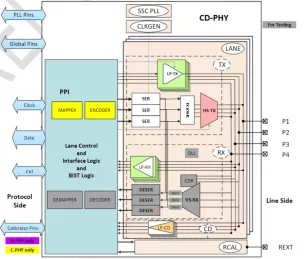

MIPI C-PHY/D-PHY Combo Universal IP, 4.5Gsps/4.5Gbps in TSMC 22ULP

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v1.2

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

MIPI D-PHY Universal IP in UMC 28HPC+

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

- Embedded, high performance, and highly programmable PLL

- Supports both low-power mode and high speed mode with integrated SERDES