SAMSUNG 11nm Flip-Chip IO library with dynamically switchable 1.8V/3.3V GPIO with fail-safe capability, 5V I2C / SMBUS open-drain cell, 5V OTP cell, 1.8V & 3.3V analog cells, and associated ESD.

A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation. The GPIO cell can be configured as input, output, open-source, or open-drain with an optional internal 50K ohm pull-up or pull-down resistor. Four selectable drive strengths are offered (25-235MHz @ 1.8V, 10pF) to optimize across SS) currents & power. The output driver exhibits 50? (±20%) termination across PVT to reduce reflections at higher operating frequencies. Supply cells for VDDIO, VREF, and core VDD include necessary built-in ESD circuitry. A 5V I2C / SMBUS open-drain (fail-safe) cell, 5V OTP, programming gate cell and 1.8V & 3.3V analog cells with ESD protection are included. The library features protection break cells to allow for separate grounds while maintaining ESD robustness. ESD design targets 2kV HBM, & 500V CDM, yet this library has constantly demonstrated 4kV HBM. This library can also support 2kV IEC 6100-4-2 system ESD with appropriate integration.

1.8V/3.3V Switchable GPIO With 5V I2C Open - Drain & Analog Cells in Samsung 11nm LPP

Overview

Key Features

- Multi-voltage 1.8V / 3.3V switchable operation

- 4 selectable drive strengths (25-235 MHz @ 1.8V, 10pF

- Full-speed output enable

- Independent power sequencing

- 50? (±20%) source termination across PVT

- Schmitt trigger receiver

- 50K? selectable pull-up or pull-down resistor

- ESD: 2kV HBM, 500V CDM, 2kV IEC 61000-4-2

- Silicon Proven

Benefits

- Area-efficient

- Dynamic multi-voltage operation

- Selectable drive strengths

- Customizable

- Pull-up / pull-down resistor options

- Feature-rich

- Robust

- Open-drain & analog cells

- 30um flip-chip cell pitch

- Silicon proven

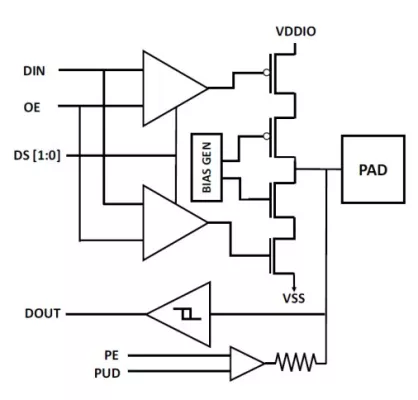

Block Diagram

Applications

- RGMII, EMMC, SD, LVCMOS, GPIO, I2C, DDC, CEC, HPD, MIPI, and various other standards

Deliverables

- GDS

- CDL netlist

- Verilog stub

- Verilog behavioral model

- LEF

- Liberty Timing Files

- IBIS (option)

- Electrical datasheet

- User guide and application notes

- Consulting and Support

Technical Specifications

Foundry, Node

Samsung 11nm

Maturity

Silicon-Proven

Availability

Immediate

Related IPs

- 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16/12nm

- 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm

- 1.0-3.3V GPIO With I2C Open Drain And 3.3V & 5V Analog Cells in 55nm

- 28nm Wirebond IO library with dynamically switchable 1.8V/ 3.3V GPIO, 5V I2C open-drain, 1.8V & 3.3V analog, OTP program cell, and HDMI & LVDS protection macros - featured across a variety of metal stack and pad configuration options

- A 65nm Wirebond IO library with 1-3.3V GPIO, 3.3V pulse-width modulation cell, I2C & SVID open-drain, 3.3V & 5V analog and OTP program cell

- A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell