MIPI C-PHY/D-PHY Combo Universal IP, 4.5Gsps/4.5Gbps in TSMC 22ULP

Overview

The MXL-CD-PHY-UNIV-T-22ULP is a high-frequency, low-power, low-cost, source-synchronous, physical Layer supporting the MIPI Alliance Specification for D-PHY v2.5 and C-PHY v2.0 The PHY can be configured as a MIPI Master or MIPI Slave supporting camera interface CSI-2 and display interface DSI/DSI-2. The PHY supports mobile, IoT, virtual reality, and automotive applications.

Key Features

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

- Consists of 3 Data lanes in C-PHY mode

- Embedded, high performance, and highly programmable PLL

- PLL supports SSC mode, Fractional mode, and Integer mode

- Supports both low-power mode and high speed mode with integrated SERDES

- 80 Mbps to 1.5 Gbps data rate per lane without Deskew calibration in D-PHY mode

- 4.5 Gbps data rate per lane with Deskew calibration in high speed D-PHY mode

- 80 Msps to 4.5 Gsps symbol rate per lane in high speed C-PHY mode

- Supports High Speed TX De-emphasis Equalization

- Supports High Speed RX CTLE

- Supports High Speed Reverse Communication

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Testability support including internal loopback

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Supports full-speed loopback testability for high-volume manufacturing tests

- Calibrator for resistance termination

Benefits

- Mixel’s MIPI C-PHY v2.0 supports a speed of 4.5 Gsps per trio, an equivalent data rate of 10.26 Gbps/trio. In D-PHY mode, the IP supports speeds up to 4.5 Gbps per lane and complies with the MIPI D-PHY v2.5 specification. With up to three trios in C-PHY and up to four lanes in D-PHY, the combo IP reaches an aggregate bandwidth of 30.78 Gbps and 18Gbps in their respective modes.

- The Mixel MIPI C-PHY/D-PHY Combo IP includes many new features to both the D-PHY and C-PHY that was not available in previous versions of the specifications, namely Spread Spectrum Clocking (SSC), transmit equalization (de-emphasis), and receiver ISI calibration. It also supports new power saving functionality such as HS-TX reduced swing modes and the HS-RX unterminated mode. The new Alternate LP Mode, suitable for IoT applications with long channels, is also supported, enabling Fast Bus Turnaround that boosts transmission bandwidth in the reverse direction of the MIPI link. The ALP Mode is central to the CSI-2 Unified Serial Link feature that reduces number of interface wires and helps to natively support longer reach. The combo PHY IP not only shares the serial interface pins, but Mixel’s implementation also reuses all the MIPI D-PHY functional blocks for the MIPI C-PHY, minimizing area and leakage power.

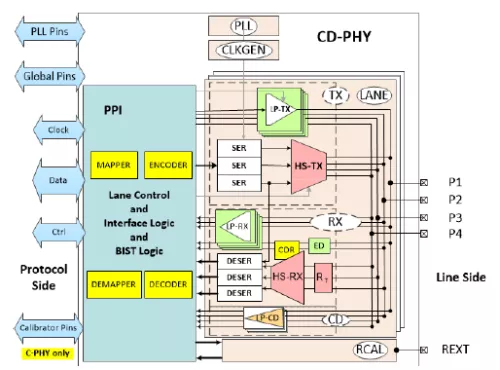

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

TSMC 22ULP

Maturity

Silicon Proven

Availability

Now

Related IPs

- MIPI C-PHY/D-PHY Combo CSI-2 TX+ IP 4.5Gsps/4.5Gbps

- NFC Semiconductor IP - Combo (digital & analog)

- I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

- MIPI C-PHY-D-PHY Combo PHY IP on TSMC 28nm HPC+

- MIPI C-PHY/D-PHY Combo Universal IP in UMC 40LP

- MIPI D-PHY Universal IP in TSMC 22ULP