MIPI C-PHY/D-PHY Combo RX IP 4.5Gsps/4.5Gbps in TSMC N7

Overview

The MXL-CDPHY-4p5G-CSI-2-RX-T-N7FF is a high-frequency, low-power, low-cost, source-synchronous, physical Layer supporting the MIPI Alliance Specification for D-PHYv2.5 and C-PHYv2.0. The PHY can be configured as a MIPI Slave supporting camera interface CSI-2. The PHY supports mobile, IoT, virtual reality, and automotive applications

Key Features

- Dual mode PHY Supports MIPI Alliance Specification D-PHYv2.5 & C-PHYv2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHYmode

- Consists of 3 Data lanes in C-PHYmode

- Supports both low-power mode and high speed mode with integrated SERDES

- 80 Mbps to 1.5 Gbps data rate per lane without skew calibration in D-PHYmode

- 4.5 Gbps data rate per lane with skew calibration in high speed D-PHYmode

- 80 Msps to 4.5 Gsps symbol rate per lane in high speed C-PHYmode

- Supports High Speed RX CTLE

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Testability support

- Calibrator for resistance termination

Benefits

- Mixel’s MIPI C-PHY v2.0 supports a speed of 4.5 Gsps per trio, an equivalent data rate of 10.26 Gbps/trio. In D-PHY mode, the IP supports speeds up to 4.5 Gbps per lane and complies with the MIPI D-PHY v2.5 specification. With up to three trios in C-PHY and up to four lanes in D-PHY, the combo IP reaches an aggregate bandwidth of 30.78 Gbps and 18Gbps in their respective modes.

- The Mixel MIPI C/D-PHY IP is area-optimized to support MIPI CSI-2 RX.

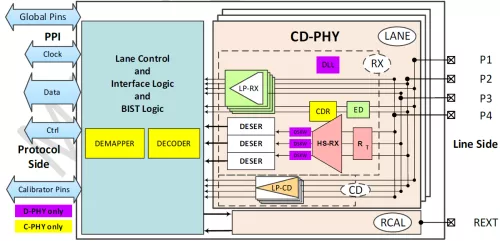

Block Diagram

Applications

- Mobile

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

TSMC N7, 7nm

Maturity

Available Upon Request

Availability

Now

TSMC

Pre-Silicon:

7nm

Related IPs

- MIPI C-PHY/D-PHY Combo CSI-2 TX+ IP 4.5Gsps/4.5Gbps

- MIPI C-PHY/D-PHY combo Rx

- HDMI 2.0/MHL RX Combo 1P PHY 6Gbps in TSMC 28nm HPC 1.8V, North/South Poly Orientation

- NFC Semiconductor IP - Combo (digital & analog)

- I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

- MIPI C-PHY-D-PHY Combo PHY IP on TSMC 28nm HPC+