MIPI I3C IP

MIPI I3C® IP is a scalable, medium-speed, utility and control bus interface for connecting peripherals to an application processor, streamlining integration and improving cost efficiencies. It gives developers unprecedented opportunities to craft innovative designs for any mobile product—from smartphones, to wearables, to systems in automobiles.

Designed as the successor of I2C, MIPI I3C incorporates key attributes of the traditional I2C and SPI interfaces to provide a unified, high-performing, very-low-power solution and delivers a robust, flexible upgrade path to I3C for I2C and SPI implementers. While I3C v1.0 delivered new capabilities to integrate mechanical, motion, biometric, environmental and any other type of sensor, updates to the specification have added new features for peripheral command, control and communication to a host processor over a short distance and system manageability.

-

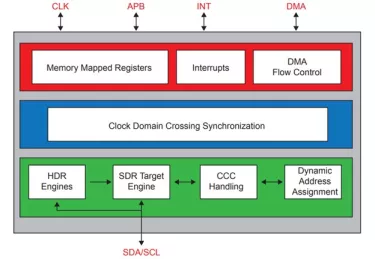

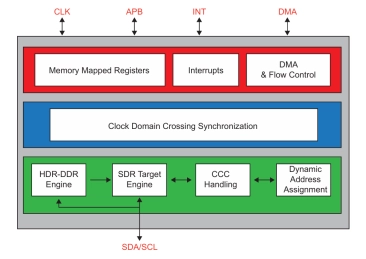

I3C V1.1 Advanced Controller

- The I3C Advanced Controller is a highly configurable I3C controller that can be used in microcontroller-based environments to provide I3C connectivity to any device.

- It contains controller capabilities as well as many of the same features as the I3C Advanced Target.

-

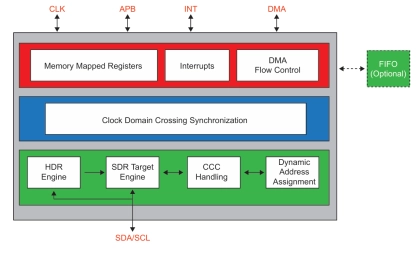

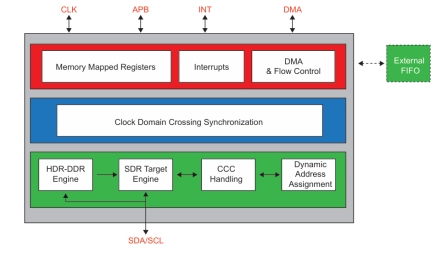

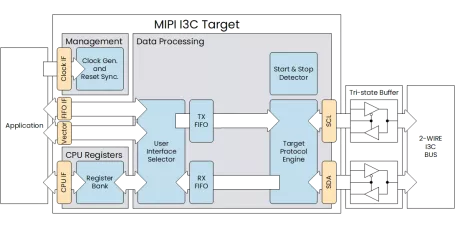

I3C V1.1 Advanced Target

- The I3C Advanced Target is a highly configurable I3C Target that can be used in microcontroller based environments to provide I3C connectivity to any device.

- It can be configured in a number of different ways to allow the core to use the minimum amount of logic to reduce both area (cost) and power.

-

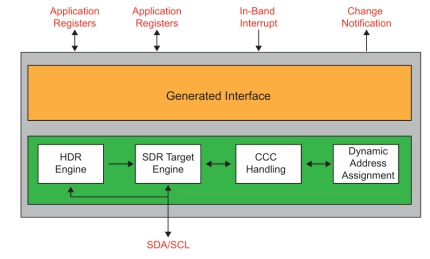

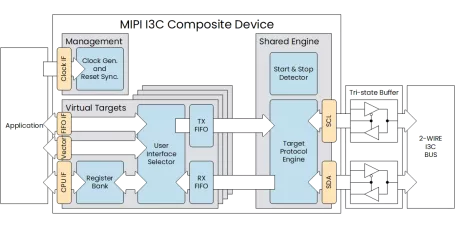

I3C V1.1 Autonomous Target

- The I3C Autonomous Target is intended for simple, data acquisition types of applications where a microprocessor is not needed to process the data.

- Instead, data is exchanged via a simple set of register interfaces to the application and the controller autonomously manages all of the communication to an upstream I3C Controller.

-

I3C Advanced Target Lite

- Advanced I3C features

- Hot join

- In-band interrupts

- Timing Control

-

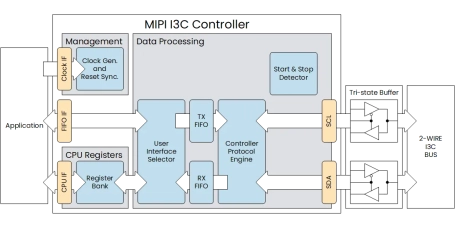

I3C Advanced Controller Lite

- The I3C Advanced Controller Lite is a highly configurable I3C controller that can be used in microcontroller-based environments to provide I3C connectivity to any device.

- It contains controller capabilities as well as many of the same features as the I3C Advanced Target.

- It can be configured in a number of different ways to allow the core to use the minimum amount of logic to reduce both area (cost) and power.

-

-

-

-

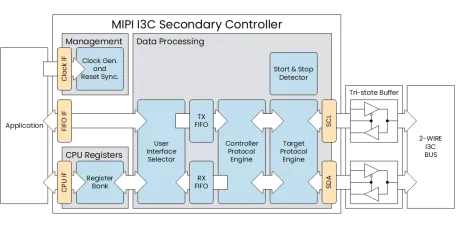

MIPI I3C Secondary Controller IP core

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, and Test Script.

- Basic RTL Test Bench

- Synthesis Scripts

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report, Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

-

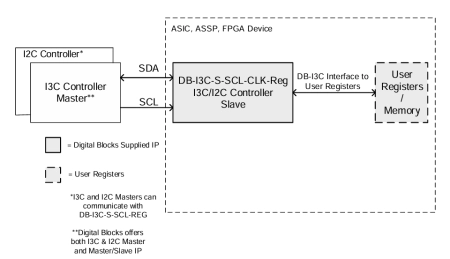

I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required

- The DB-I3C-S-SCL-CLK-REG is an I3C Slave Controller IP Core focused on low power, low noise, low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no free running clock.

- The DB-I3C-S-SCL-CLK-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-SCL-CLK-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec-ver1_0 specification.