UFS IP

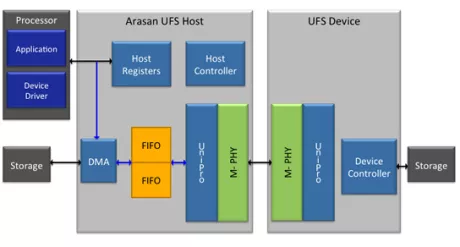

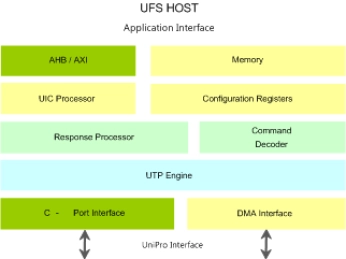

The Universal Flash Storage (UFS) Host Controller IP is a standard-based serial interface engine for implementing the JEDEC UFS interface in compliance with the JEDEC UFS, UFS Host Controller Interface (UFSHCI) standards as well as the UFS removable card v1.1 standards.

UFS stands for "Universal Flash Storage." It is a type of non-volatile memory used in many mobile devices, such as smartphones and tablets, as well as in some digital cameras and other electronics.

All offers in

UFS IP

Filter

Compare

32

UFS IP

from 9 vendors

(1

-

10)

-

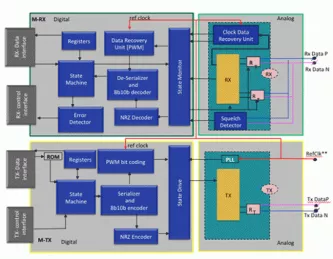

MIPI M-PHY G4 Designed For TSMC 28nm HPC+

- Compliant to MIPI Alliance Standard for M-PHY specification Version 4.1

- Supports M-PHY Type-I system

- Support for Clock and Data Recovery Options

-

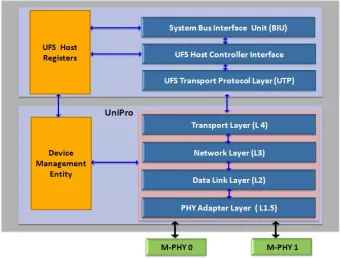

UFS 3.0 Host Controller compatible with M-PHY 4.0 and UniPro 1.8

- UFS 3.0 Host and Device configurations available

- Complete UFS 3.0 hardware implementation

- Interop-proven UniPro 1.8 link layer

-

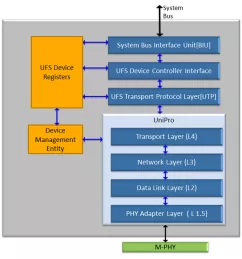

UFS 2.1 Device Controller compatible with MIPI M-PHY 3.1 and UniPro 1.6

- Compliant with JESD220B UFS 2.0

- MIPI UniPro version 1.6

- High-performance M-PHY v3.0 type 1

-

UFS 2.1 Host Controller compatible with M-PHY 3.1 and UniPro 1.6

- JEDEC UFS 2.0 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.0 type-1

- 2 lanes @ 5.9 Gbps per lane

-

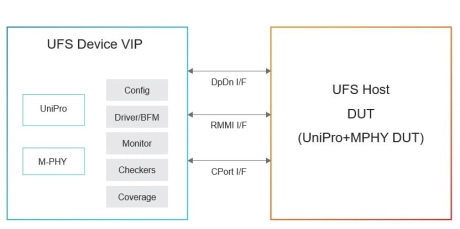

UFS Controller - Verifies compliance and performance of UFS interfaces in SoCs

- The UFS Controller Verification IP (VIP) ensures proper operation and compliance of UFS interfaces in SoC designs. It supports UFS 2.0, 2.1, 3.0, and 3.1 standards, enabling efficient validation of high-speed data transfers and power management.

- The VIP is critical for validating UFS controllers in a wide range of applications, from AI/ML systems to mobile devices and automotive infotainment. It ensures optimal performance, reliability, and seamless integration in diverse environments

-

Simulation VIP for UFS

- Interfaces

- DPDN I/F and RMMI I/F when used with UniPro VIP. CPort signaling pin I/F and CPort message using transactions

- UTP Layer - UPIUs

- NOP IN, NOP OUT, Query Request/ Response, Task Management Request/ Response, Command, Response, Data Out, Data In

-

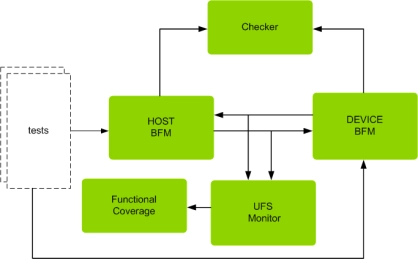

UFS Verification IP

- Full UFS Host and Device functionality.

- Compliant testsuite as per JESD224 document.

- Supports high performance M-PHY type-1

- Supports full UFS Host and Device functionality.

-

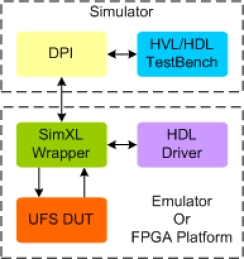

UFS Synthesizable Transactor

- Full UFS Host and Device functionality

- Supports UFS 2.1 draft specification

- Supports high performance M-PHY type-1

- Supports full UFS Host and Device functionality

-

UFS HOST Controller IIP

- Supports high performance M-PHY type-1.

- Supports full UFS Host functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport.

-

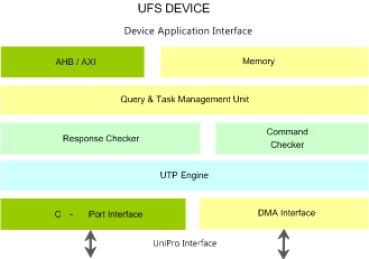

UFS DEVICE IIP

- Supports high performance M-PHY type-1.

- Supports full UFS Device functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport