MIPI IP for UMC

Welcome to the ultimate MIPI IP for UMC hub! Explore our vast directory of MIPI IP for UMC

All offers in

MIPI IP

for UMC

Filter

Compare

59

MIPI IP

for UMC

from 9 vendors

(1

-

10)

-

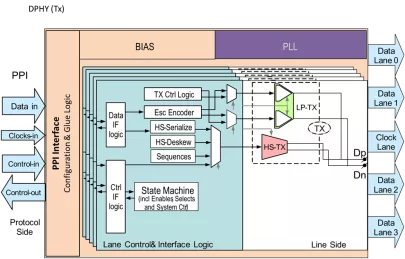

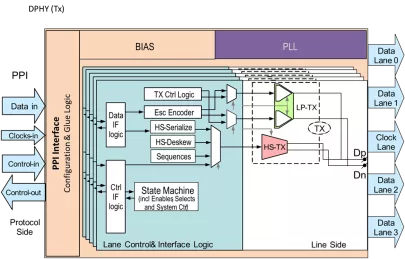

MIPI D-PHY Universal IP in UMC 28HPC+

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

- Embedded, high performance, and highly programmable PLL

- Supports both low-power mode and high speed mode with integrated SERDES

-

MIPI DPHY v1.2 TX 4 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY v1.2 RX 4 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Tx 2 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Rx 2 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Tx 4 Lanes - UMC 22ULP 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Rx 4 Lanes - UMC 22ULP 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

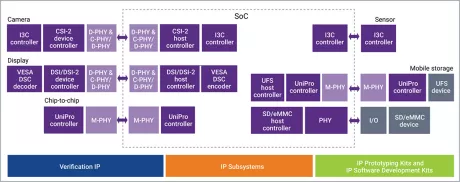

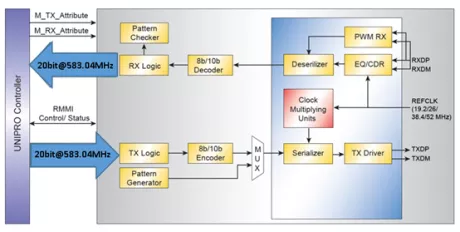

MIPI MPHY v3.1, 2Tx-2Rx Type-1, UMC 22ULL 1.8V, N/S orientation

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

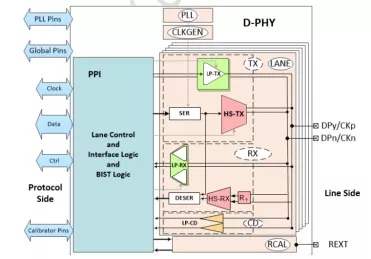

MIPI DPHY_RX v1.2, 2C4D, UMC 28HPC+, E/W orientation

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

MIPI DPHY_TX v1.2, 1C4D, UMC 28HPC+, E/W orientation

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes