PCI Express Phy IP for TSMC

Welcome to the ultimate PCI Express Phy IP for TSMC hub! Explore our vast directory of PCI Express Phy IP for TSMC

All offers in

PCI Express Phy IP

for TSMC

Filter

Compare

119

PCI Express Phy IP

for TSMC

from 10 vendors

(1

-

10)

-

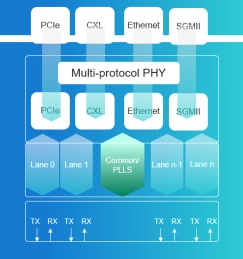

PHY for PCIe 5.0 and CXL

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Advanced equalization and clock-data-recovery to deliver unmatched channel loss handling performance and reliability

- Eye Surf —provides convenient access to an integrated non-destructive real-time eye scope and BER bathtub curve to monitor the bit error rate (BER) and the link performance during live traffic

-

10G PHY for PCIe 2.0, TSMC 7FF x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

10G PHY for PCIe 2.0, TSMC 7FF x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY LP18, TSMC 28HPCP x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 LP PHY, TSMC 28HPCP x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, TSMC 28HPC+ x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, TSMC 28HPC+ x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, TSMC 28HPC+ x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, TSMC 28HPC x8, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, TSMC 28HPC x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island