DLL IP for SMIC

Welcome to the ultimate DLL IP for SMIC hub! Explore our vast directory of DLL IP for SMIC

All offers in

DLL IP

for SMIC

Filter

Compare

10

DLL IP

for SMIC

from 4 vendors

(1

-

10)

-

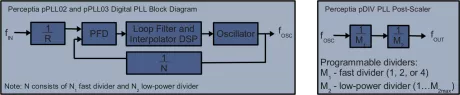

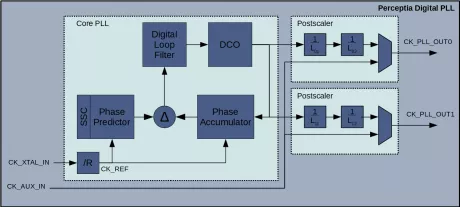

High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- Fractional-N digital PLL architecture, using an LC-tank oscillator

-

Low Voltage, Low Power Fractional-N PLLs

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

General Purpose Fractional-N PLLs

- Low power, suitable for logic clocking applications

- Extremely small die area, using a ring oscillator

- Twelve bits fractional resolution

-

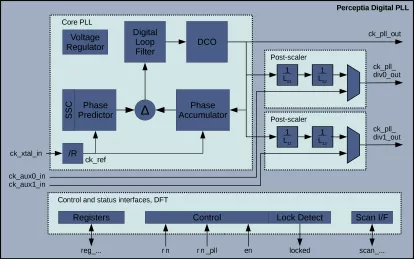

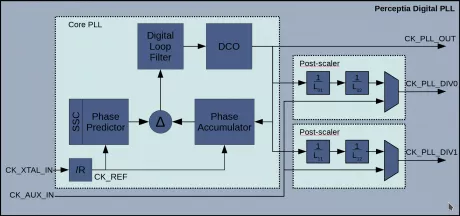

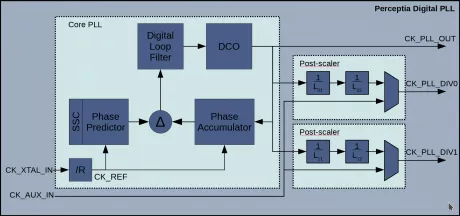

4-GHz Jitter-optimized low-power digital PLL

- - Jitter below 10-ps

- - Super small: 90 x 90 microns!

- - Very low power: 15-mW

- - Broad frequency range: 4-GHz

-

Minimum-area low-power clocking PLL (1st gen)

- - Super small: 80 x 80 microns!

- - Very low power: 12-mW

- - Broad frequency range: 2-GHz

- - Fast lock

-

100~450MHz DDR DLL with 80 Phase Selection, SMIC0.1.3um

- Master-Slave structured DLL

- Delivers optimized small jitter frequencies

- 0-80 phase selection

- Ultra small size (<.1mm^2) suitable to multiple-usage integration

-

Slaver DLL

- Core power supply: 0.9V

- Area: 0.0051mm2 (170um*30um)

- Reference clock frequency range from 200MHz to 800MHz

- Output clock phase:0/90/180/270

-

Master DLL

- Core power supply: 0.9V

- Area: 0.0086mm2 (260.35um*33.08um)

- Reference clock frequency range from 200MHz to 800MHz

- Output clock phase:0/90/180/270

-

4-GHz Jitter-optimized low-power digital PLL

- Jitter below 10-ps

- Super small: 90 x 90 microns!

- Very low power: 15-mW

-

SMIC 0.13um DLL

- 4-channel outputs with 45 degree (90, 135, 180, 225, 270, 315 degree optional) phase

- shift of the period of CLK_DLL

- Rise time matches fall time on the output signal’s edges

- Lock in time: less than 10us